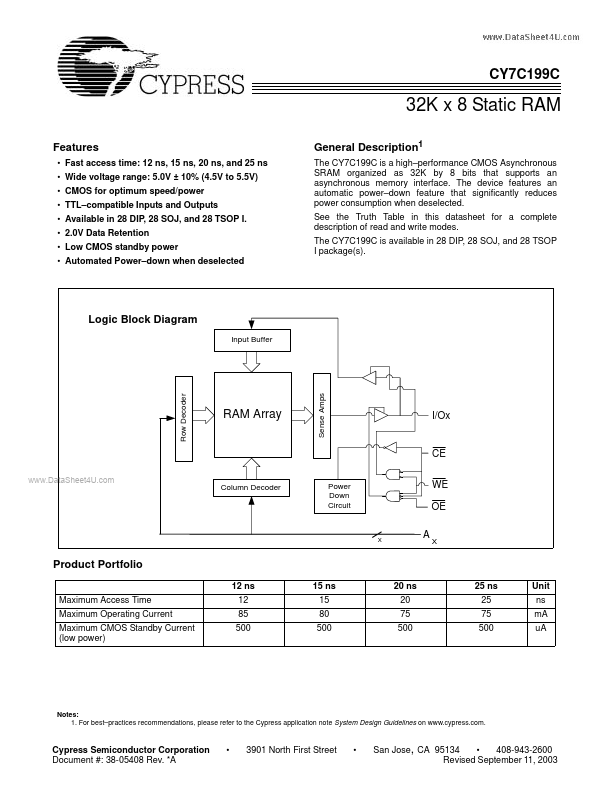

CY7C199C Overview

Key Specifications

Package: TSSOP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Key Features

- Fast access time: 12 ns, 15 ns, 20 ns, and 25 ns

- Wide voltage range: 5.0V ± 10% (4.5V to 5.5V)

- CMOS for optimum speed/power

- TTL–compatible Inputs and Outputs

- Available in 28 DIP, 28 SOJ, and 28 TSOP I

- 2.0V Data Retention

- Low CMOS standby power

- 3901 North First Street

- San Jose, CA 95134