CY7C1352F

CY7C1352F is 4-Mbit (256K x 18) Pipelined SRAM manufactured by Cypress.

4-Mbit (256Kx18) Pipelined SRAM with No BL™ Architecture

Features

- Pin patible and functionally equivalent to ZBT™ devices

- Internally self-timed output buffer control to eliminate the need to use OE

- Byte Write capability

- 256K x 18 mon I/O architecture

- Single 3.3V power supply

- 2.5V / 3.3V I/O Operation

- Fast clock-to-output times

- 2.6 ns (for 250-MHz device)

- 2.6 ns (for 225-MHz device)

- 2.8 ns (for 200-MHz device)

- 3.5 ns (for 166-MHz device)

- 4.0 ns (for 133-MHz device)

- 4.5 ns (for 100-MHz device)

- Clock Enable (CEN) pin to suspend operation

- Synchronous self-timed writes

- Asynchronous output enable (OE)

- JEDEC-standard 100 TQFP package

- Burst Capability- linear or interleaved burst order

- “ZZ” Sleep Mode Option and Stop Clock option

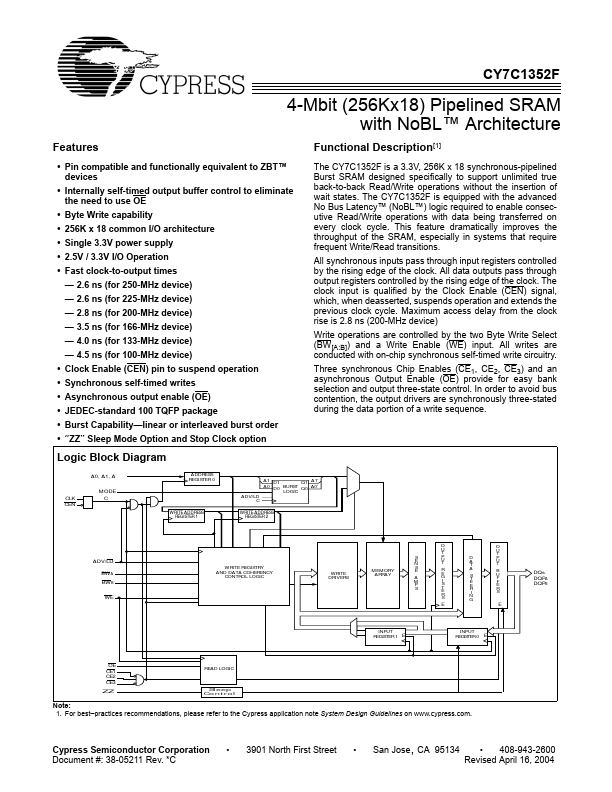

Logic Block Diagram

Functional Description[1]

The CY7C1352F is a 3.3V, 256K x 18 synchronous-pipelined Burst SRAM designed specifically to support unlimited true...