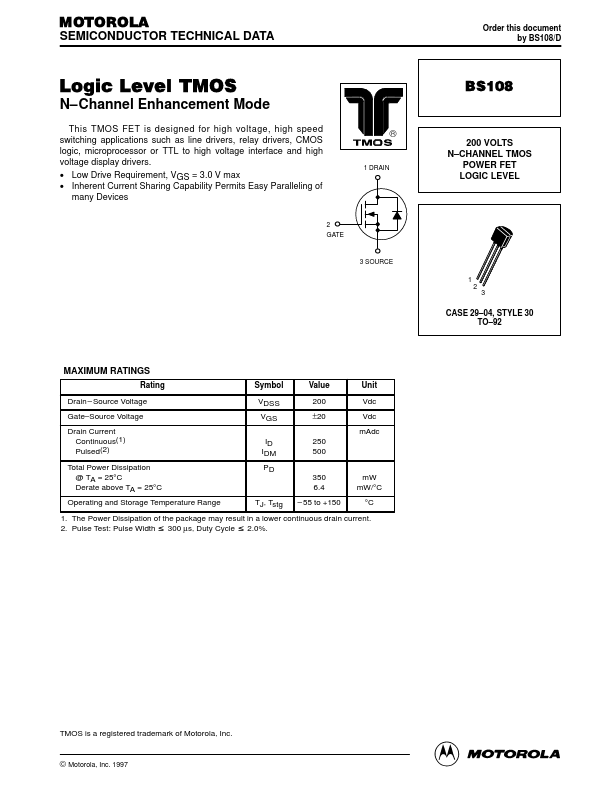

BS108

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by BS108/D

Logic Level TMOS

®

1 DRAIN

N- Channel Enhancement Mode

This TMOS FET is designed for high voltage, high speed switching applications such as line drivers, relay drivers, CMOS logic, microprocessor or TTL to high voltage interface and high voltage display drivers.

- Low Drive Requirement, VGS = 3.0 V max

- Inherent Current Sharing Capability Permits Easy Paralleling of many Devices

2 GATE 3 SOURCE

1 2 3

200 VOLTS N- CHANNEL TMOS POWER FET LOGIC LEVEL

CASE 29- 04, STYLE 30 TO- 92

MAXIMUM RATINGS

Rating Drain

- Source Voltage Gate- Source Voltage Drain Current Continuous(1) Pulsed(2) Total Power Dissipation @ TA = 25°C Derate above TA = 25°C Operating and Storage Temperature Range Symbol VDSS VGS ID IDM PD 350 6.4 TJ, Tstg

- 55 to +150 m W m W/°C °C Value 200 ±20 250 500 Unit Vdc Vdc m Adc

1. The Power Dissipation of the package may result in a lower continuous drain current. 2. Pulse Test: Pulse Width 300 µs,...