CY7C135A

Features

- True dual-ported memory cells, which allow simultaneous reads of the same memory location

- 4K x 8 organization

- 0.65 micron CMOS for optimum speed and power

- High speed access: 15 ns

- Low operating power: ICC = 160 m A (max)

- Fully asynchronous operation

- Automatic power down

- Semaphores included on the 7C1342 to permit software handshaking between ports

- Available in 52-pin PLCC

- Pb-free packages available

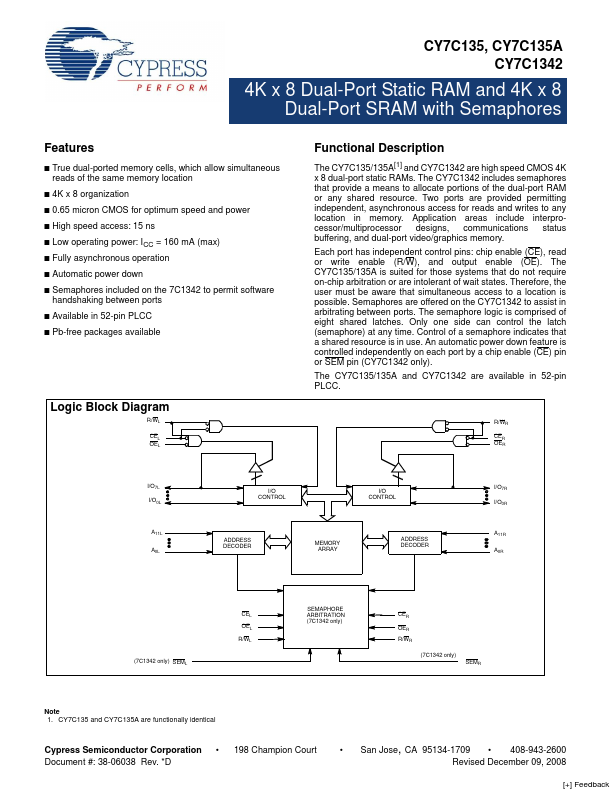

Logic Block Diagram

R/WL CEL OEL

Functional Description

The CY7C135/135A[1] and CY7C1342 are high speed CMOS 4K x 8 dual-port static RAMs. The CY7C1342 includes semaphores that provide a means to allocate portions of the dual-port RAM or any shared resource. Two ports are provided permitting independent, asynchronous access for reads and writes to any location in memory. Application areas include interprocessor/multiprocessor designs,...