MC100ES8111 Description

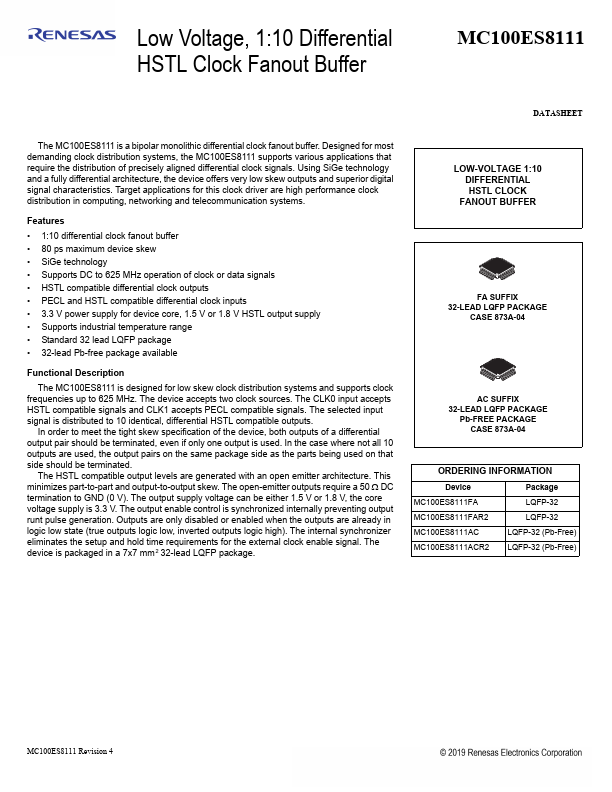

The MC100ES8111 is designed for low skew clock distribution systems and supports clock frequencies up to 625 MHz. The device accepts two clock sources. The CLK0 input accepts HSTL patible signals and CLK1 accepts PECL patible signals.

MC100ES8111 Key Features

- 1:10 differential clock fanout buffer

- 80 ps maximum device skew

- SiGe technology

- Supports DC to 625 MHz operation of clock or data signals

- HSTL patible differential clock outputs

- PECL and HSTL patible differential clock inputs

- 3.3 V power supply for device core, 1.5 V or 1.8 V HSTL output supply

- Supports industrial temperature range

- Standard 32 lead LQFP package

- 32-lead Pb-free package available