PA7540

Description

The PA7540 is a member of the Programmable Electrically Erasable Logic (PEEL™) Array family based on ICT’s CMOS EEPROM technology.

Key Features

- The PA7540 supports speeds as fast as 10ns/15ns (tpdi/tpdx) and 71.46MHz (fMAX) at moderate power consumption 80mA (55mA typical)

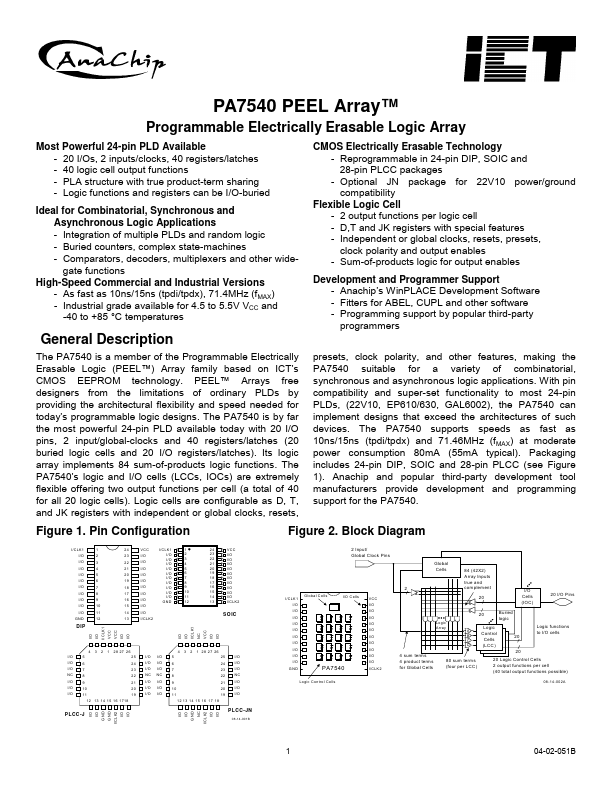

- Packaging includes 24-pin DIP, SOIC and 28-pin PLCC (see Figure 1)

- Anachip and popular third-party development tool manufacturers provide development and programming support for the PA7540