74LS73

Description

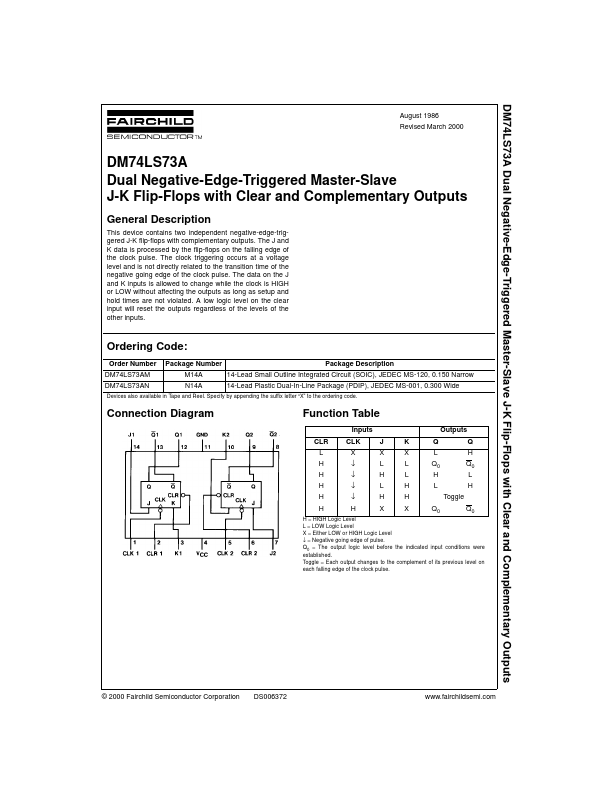

This device contains two independent negative-edge-triggered J-K flip-flops with plementary outputs. The J and K data is processed by the flip-flops on the falling edge of the clock pulse. The clock triggering occurs at a voltage level and is not directly related to the transition time of the negative going edge of the clock pulse. The data on the J and K inputs is allowed to change while the clock is HIGH or LOW without affecting the outputs as long as setup and hold times are not violated. A low logic level on the clear input will reset the outputs regardless of the levels of the other inputs.

Ordering Code:

Order Number DM74LS73AM DM74LS73AN Package Number M14A N14A Package Description

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Function...