74LS74

SN74LS74A Dual D-Type Positive Edge-Triggered Flip-Flop

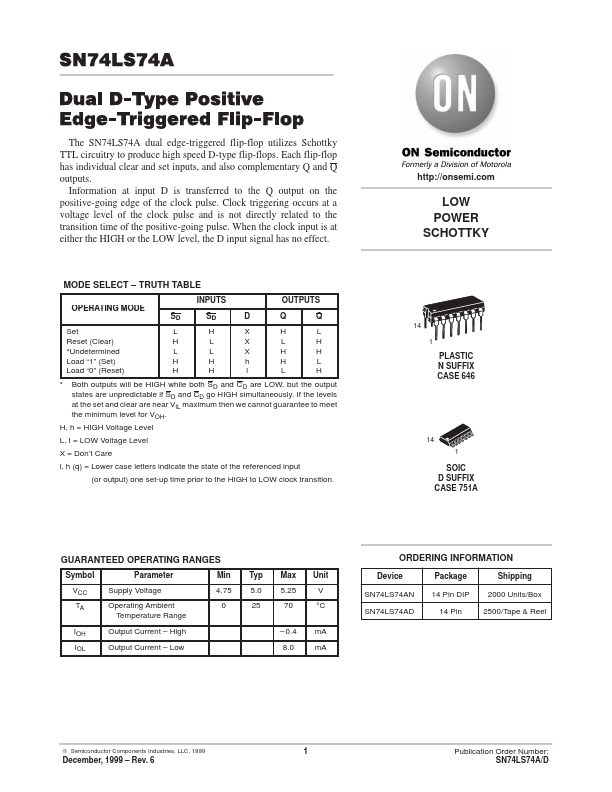

The SN74LS74A dual edge-triggered flip-flop utilizes Schottky TTL circuitry to produce high speed D-type flip-flops. Each flip-flop has individual clear and set inputs, and also plementary Q and Q outputs. Information at input D is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the HIGH or the LOW level, the D input signal has no effect. http://onsemi.

LOW POWER SCHOTTKY

MODE SELECT

- TRUTH TABLE

INPUTS OPERATING MODE SD Set Reset (Clear)

- Undetermined Load “1” (Set) Load “0” (Reset)

- L H L H H SD H L L H H D X X X h l Q H L H H L Q L H H L H

14 1

OUTPUTS

PLASTIC N SUFFIX CASE 646

Both outputs will be HIGH while both SD and CD are LOW, but the output states are unpredictable if SD and CD go HIGH simultaneously. If the...