AS7C1024A

Features

- AS7C1024A (5V version)

- AS7C31024A (3.3V version)

- Industrial and mercial temperatures

- Organization: 131,012 words x 8 bits

- High speed

- 10/12/15/20 ns address access time

- 3/3/4/5 ns output enable access time

- Low power consumption: ACTIVE

- 660 m W (AS7C1024A) / max @ 10 ns

- 324 m W (AS7C31024A) / max @ 10 ns

- Low power consumption: STANDBY

- 55 m W (AS7C1024A) / max CMOS

- 36 m W (AS7C31024A) / max CMOS

- Latest 6T 0.25u CMOS technology

- 2.0V data retention

- Easy memory expansion with CE1, CE2, OE inputs

- TTL/LVTTL-patible, three-state I/O

- 32-pin JEDEC standard packages

- 300 mil SOJ

- 400 mil SOJ

- 8 × 20mm TSOP I

- ESD protection ≥ 2000 volts

- Latch-up current ≥ 200 m A

Row decoder Sense amp

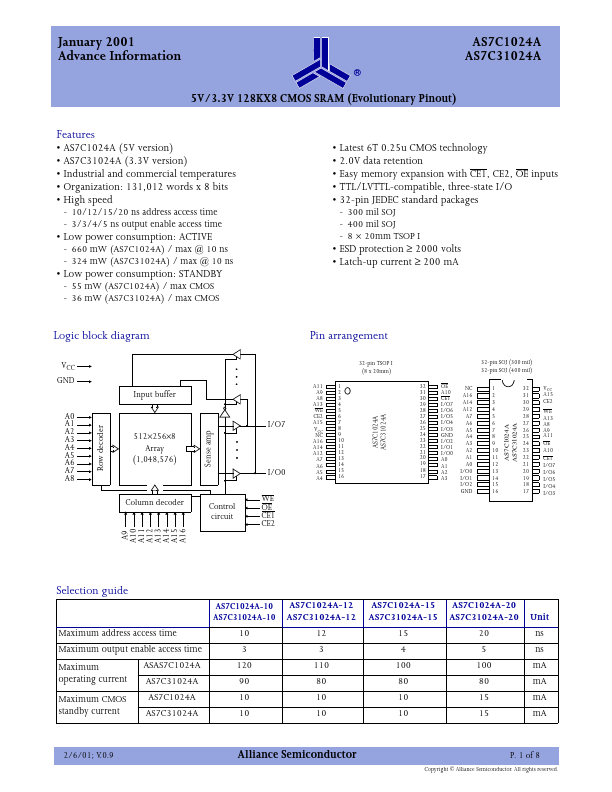

Logic block diagram

VCC GND

Input buffer

A0

A1

A2 A3

512×256×8

A4 Array

A5 A6

(1,048,576)

A7

A8

Column...