Description

1]

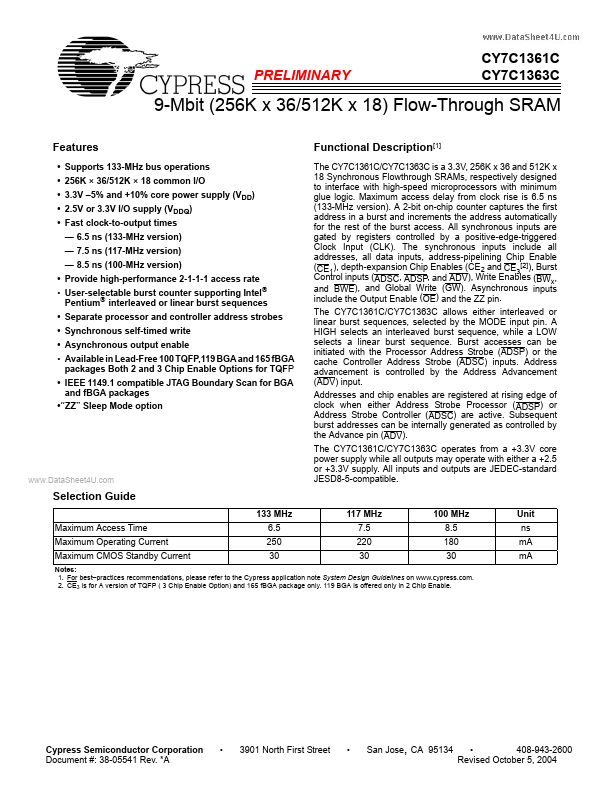

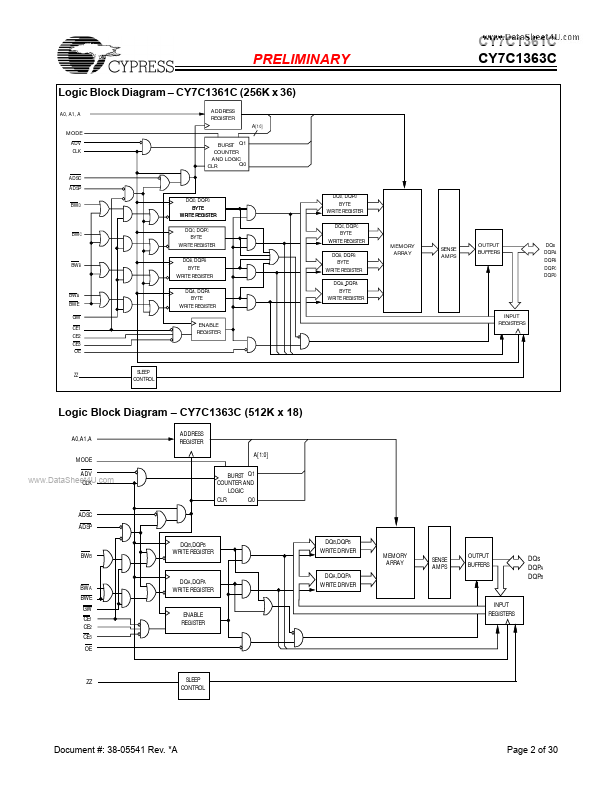

The CY7C1361C/CY7C1363C is a 3.3V, 256K x 36 and 512K x 18 Synchronous Flowthrough SRAMs, respectively designed to interface with high-speed microprocessors with minimum glue logic.Maximum access delay from clock rise is 6.5 ns (133-MHz version).A 2-bit on-chip counter captures the first address in a burst and increments the address automatically for the rest of the burst access.All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK).The syn

Features

- Supports 133-MHz bus operations.

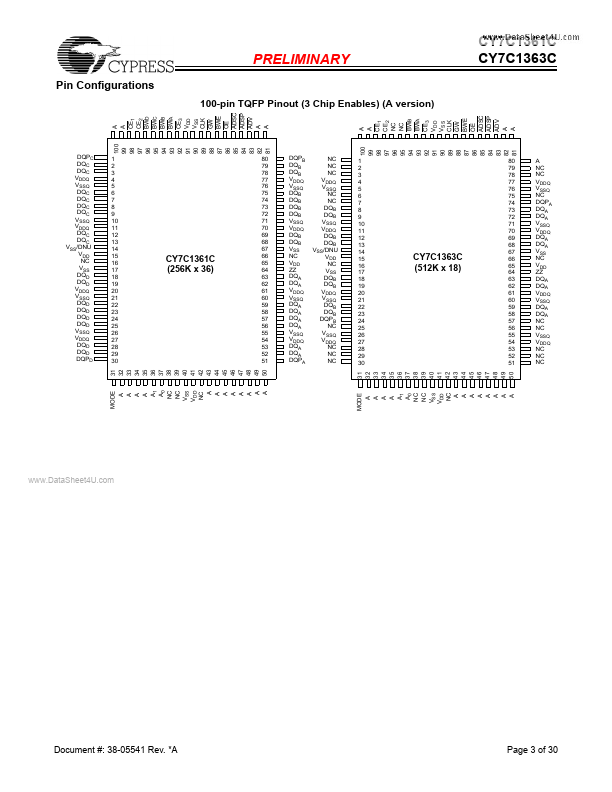

- 256K × 36/512K × 18 common I/O.

- 3.3V.

- 5% and +10% core power supply (VDD).

- 2.5V or 3.3V I/O supply (VDDQ).

- Fast clock-to-output times.

- 6.5 ns (133-MHz version).

- 7.5 ns (117-MHz version).

- 8.5 ns (100-MHz version).

- Provide high-performance 2-1-1-1 access rate.

- User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences.

- Sepa.