74VHC126

Description

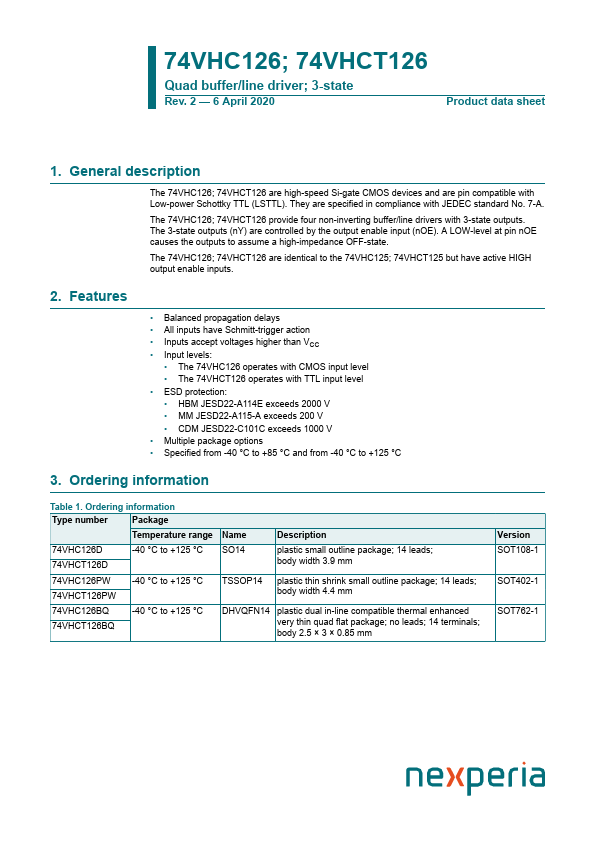

The 74VHC126; 74VHCT126 are high-speed Si-gate CMOS devices and are pin compatible with Low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard No. 7-A.

Key Features

- Balanced propagation delays

- All inputs have Schmitt-trigger action

- Inputs accept voltages higher than VCC

- Input levels:

- The 74VHC126 operates with CMOS input level

- The 74VHCT126 operates with TTL input level

- ESD protection:

- HBM JESD22-A114E exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- CDM JESD22-C101C exceeds 1000 V