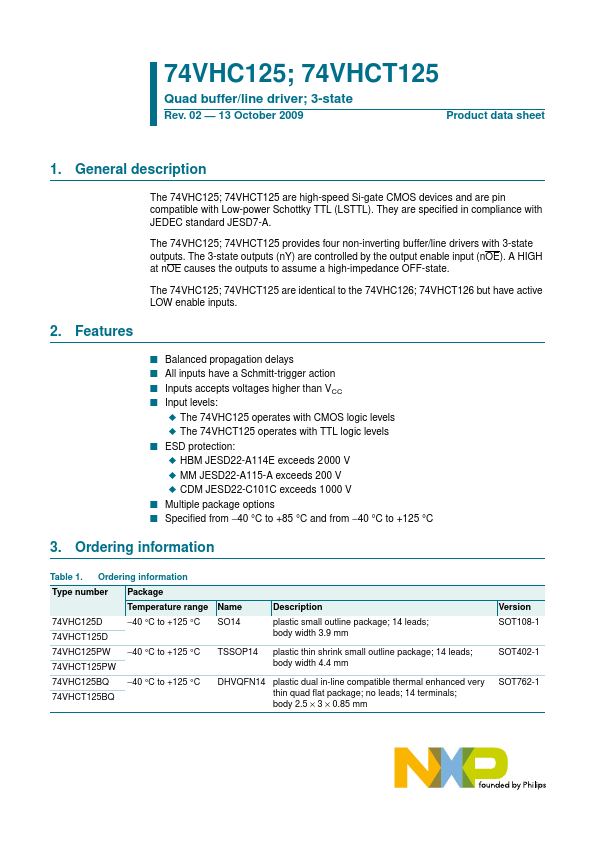

| Part | 74VHC125 |

|---|---|

| Description | Quad buffer/line driver |

| Manufacturer | NXP Semiconductors |

| Size | 83.12 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74VHC125 | Fairchild Semiconductor | Quad Buffer |

| 74VHC123A | Fairchild Semiconductor | Dual Retriggerable Monostable Multivibrator |

| 74VHC126 | Nexperia | Quad buffer/line driver |

| 74VHC126-Q100 | Nexperia | Quad buffer/line driver |