Si5383

Overview

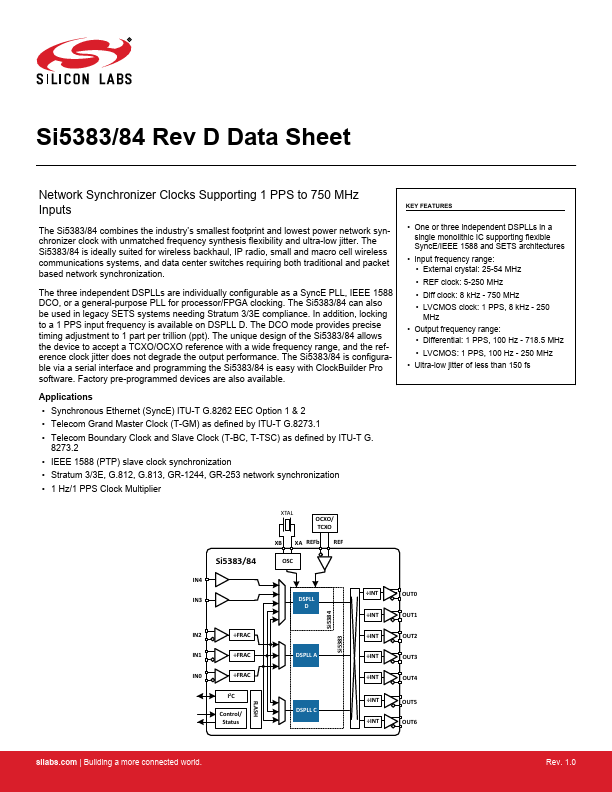

- One or three independent DSPLLs in a single monolithic IC supporting flexible SyncE/IEEE 1588 and SETS architectures

- Input frequency range:

- External crystal: 25-54 MHz

- REF clock: 5-250 MHz

- Diff clock: 8 kHz - 750 MHz

- LVCMOS clock: 1 PPS, 8 kHz - 250 MHz

- Output frequency range:

- Differential: 1 PPS, 100 Hz - 718.5 MHz

- LVCMOS: 1 PPS, 100 Hz - 250 MHz