### Si5383/84 Rev D Data Sheet

## Network Synchronizer Clocks Supporting 1 PPS to 750 MHz Inputs

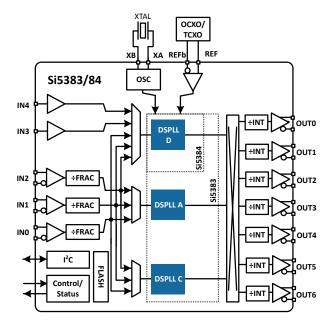

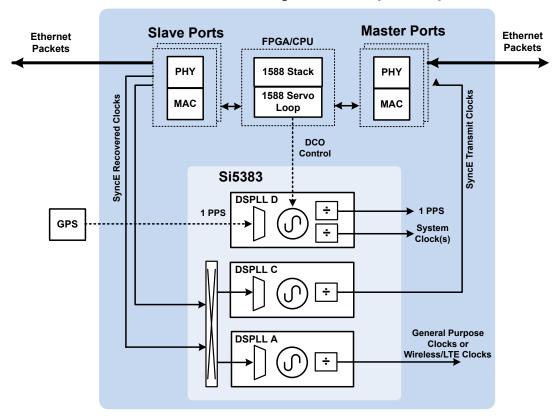

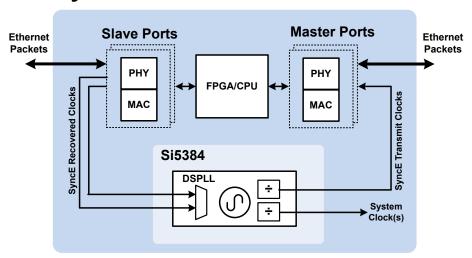

The Si5383/84 combines the industry's smallest footprint and lowest power network synchronizer clock with unmatched frequency synthesis flexibility and ultra-low jitter. The Si5383/84 is ideally suited for wireless backhaul, IP radio, small and macro cell wireless communications systems, and data center switches requiring both traditional and packet based network synchronization.

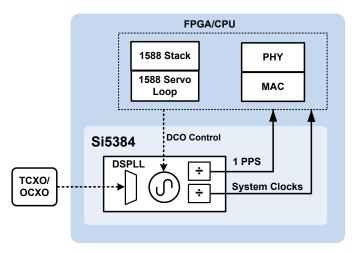

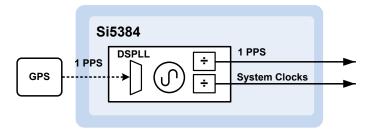

The three independent DSPLLs are individually configurable as a SyncE PLL, IEEE 1588 DCO, or a general-purpose PLL for processor/FPGA clocking. The Si5383/84 can also be used in legacy SETS systems needing Stratum 3/3E compliance. In addition, locking to a 1 PPS input frequency is available on DSPLL D. The DCO mode provides precise timing adjustment to 1 part per trillion (ppt). The unique design of the Si5383/84 allows the device to accept a TCXO/OCXO reference with a wide frequency range, and the reference clock jitter does not degrade the output performance. The Si5383/84 is configurable via a serial interface and programming the Si5383/84 is easy with ClockBuilder Pro software. Factory pre-programmed devices are also available.

#### **Applications**

- Synchronous Ethernet (SyncE) ITU-T G.8262 EEC Option 1 & 2

- · Telecom Grand Master Clock (T-GM) as defined by ITU-T G.8273.1

- Telecom Boundary Clock and Slave Clock (T-BC, T-TSC) as defined by ITU-T G. 8273.2

- IEEE 1588 (PTP) slave clock synchronization

- Stratum 3/3E, G.812, G.813, GR-1244, GR-253 network synchronization

- 1 Hz/1 PPS Clock Multiplier

#### **KEY FEATURES**

- One or three independent DSPLLs in a single monolithic IC supporting flexible SyncE/IEEE 1588 and SETS architectures

- · Input frequency range:

- External crystal: 25-54 MHz

- · REF clock: 5-250 MHz

- Diff clock: 8 kHz 750 MHz

- LVCMOS clock: 1 PPS, 8 kHz 250 MHz

- · Output frequency range:

- · Differential: 1 PPS, 100 Hz 718.5 MHz

- LVCMOS: 1 PPS, 100 Hz 250 MHz

- · Ultra-low jitter of less than 150 fs

## **Table of Contents**

| 1. | Feature List                                                                                                                                                                                                                                    | . 1               |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 2. | Ordering Guide                                                                                                                                                                                                                                  | . 2               |

|    | 2.1 Ordering Part Number Fields                                                                                                                                                                                                                 | . 2               |

| 3. | Functional Description                                                                                                                                                                                                                          | . 4               |

|    | 3.1 Standards Compliance                                                                                                                                                                                                                        | . 4               |

|    | 3.2 Frequency Configuration                                                                                                                                                                                                                     | . 4               |

|    | 3.3 DSPLL Loop Bandwidth in Standard Input Mode                                                                                                                                                                                                 |                   |

|    | 3.4 DSPLL Loop Bandwidth in 1 PPS Mode                                                                                                                                                                                                          |                   |

|    | 3.5 Modes of Operation .       .         3.5.1 Initialization and Reset .       .         3.5.2 Free-run Mode .       .         3.5.3 Lock Acquisition Mode .       .         3.5.4 Locked Mode .       .         3.5.5 Holdover Mode .       . | . 5<br>. 6<br>. 6 |

|    | 3.6 Digitally-Controlled Oscillator (DCO) Mode                                                                                                                                                                                                  | . 7               |

|    | 3.7 External Reference (XA/XB, REF/REFb)                                                                                                                                                                                                        | . 9               |

|    | 3.8 Inputs (IN0, IN1, IN2, IN3, IN4)                                                                                                                                                                                                            | .11               |

|    | 3.8.3 Automatic Input Selection in Standard Input Mode                                                                                                                                                                                          |                   |

|    | 3.8.5 Hitless Input Switching in Standard Input Mode                                                                                                                                                                                            |                   |

|    | 3.8.6 Ramped Input Switching in Standard Input Mode                                                                                                                                                                                             |                   |

|    | 3.8.7 Glitchless Input Switching                                                                                                                                                                                                                |                   |

|    | 3.9 Fault Monitoring                                                                                                                                                                                                                            |                   |

|    | 3.9.1 Input LOS Detection                                                                                                                                                                                                                       |                   |

|    | 3.9.2 XA/XB LOS Detection                                                                                                                                                                                                                       |                   |

|    | 3.9.3 OOF Detection                                                                                                                                                                                                                             |                   |

|    | 3.9.4 Precision OOF Monitor                                                                                                                                                                                                                     |                   |

|    | 3.9.5 Fast OOF Monitor                                                                                                                                                                                                                          |                   |

|    | 3.9.6 LOL Detection                                                                                                                                                                                                                             | .17               |

|    | 3.9.7 Interrupt Pin (INTRb)                                                                                                                                                                                                                     | .18               |

|    | 3.10 Outputs                                                                                                                                                                                                                                    | .18               |

| 3.10.1 Output Crosspoint                                                                                  | 19 |

|-----------------------------------------------------------------------------------------------------------|----|

| 3.10.2 Support For 1 Hz Output                                                                            | 20 |

| 3.10.3 Differential Output Terminations                                                                   | 21 |

| 3.10.4 Output Signal Format                                                                               |    |

| 3.10.5 Programmable Common-Mode Voltage For Differential Outputs                                          |    |

| 3.10.6 LVCMOS Output Impedance Selection                                                                  |    |

| 3.10.7 LVCMOS Output Signal Swing                                                                         |    |

| 3.10.8 LVCMOS Output Polarity                                                                             |    |

| 3.10.9 Output Enable/Disable                                                                              |    |

| 3.10.10 Output Disable During LOL                                                                         |    |

| 3.10.12 Output Disable During XXXB_LOS                                                                    |    |

| 3.10.13 Synchronous/Asynchronous Output Disable                                                           |    |

| 3.10.14 Output Divider (R) Synchronization                                                                |    |

| 3.10.15 Programmable Phase Offset in 1 PPS Mode                                                           |    |

| 3.11 Power Management                                                                                     |    |

| 3.12 In-Circuit Programming                                                                               |    |

| 3.13 Serial Interface                                                                                     | 23 |

| 3.14 Custom Factory Preprogrammed Parts                                                                   | 23 |

| 3.15 Enabling Features and/or Configuration Settings Not Available in ClockBuilder Pro programmed Devices | •  |

| 4. Register Map                                                                                           | 25 |

| 5. Electrical Specifications                                                                              | 26 |

| 6. Typical Application Diagrams                                                                           | 38 |

|                                                                                                           |    |

| -                                                                                                         |    |

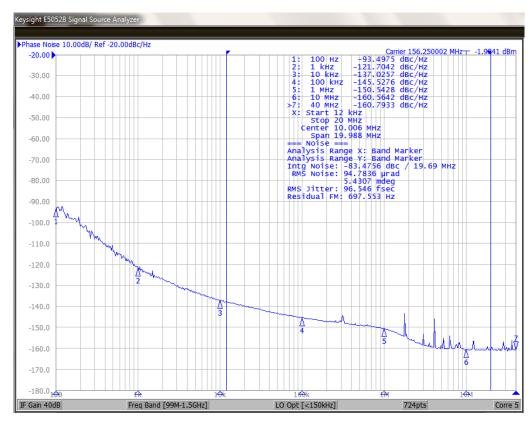

| 8. Typical Operating Characteristics (Jitter and Phase Noise)                                             | 41 |

| 9. Pin Descriptions                                                                                       | 42 |

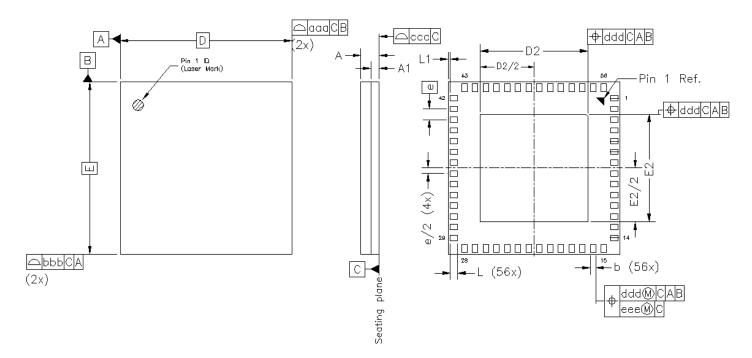

| 10. Package Outline                                                                                       | 45 |

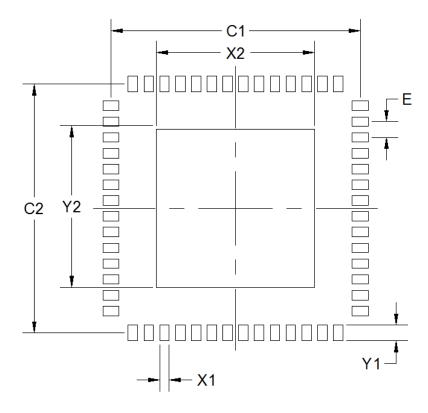

| 11. PCB Land Pattern                                                                                      | 47 |

| 12. Top Marking                                                                                           | 49 |

| 13. Device Errata                                                                                         |    |

|                                                                                                           |    |

| 14. Revision History                                                                                      | 51 |

| 14.1 Revision 0.8                                                                                         | 51 |

| 14.2 Revision 1.0                                                                                         | 51 |

#### 1. Feature List

The Si5383/84 highlighted features are listed below.

- One or three DSPLLs in a single monolithic IC supporting flexible SyncE/IEEE 1588 and SETS architectures

- · Meets the requirements of:

- ITU-T G.8273.1 T-GM

- ITU-T G.8273.2 T-BC, T-TSC

- ITU-T G.8262 (SyncE) EEC Options 1 & 2

- ITU-T G.812 Type III, IV

- ITU-T G.813 Option 1

- Telcordia GR-1244, GR-253 (Stratum-3/3E)

- Each DSPLL generates any output frequency from any input frequency

- · Input frequency range:

- External crystal: 25 54 MHz

- REF clock: 5 250 MHz

- Diff clock: 8 kHz 750 MHz

- · LVCMOS clock: 1 PPS, 8 kHz 250 MHz

- · Output frequency range:

- Differential: 1 PPS, 100 Hz 718.5 MHz

- LVCMOS: 1 PPS, 100 Hz 250 MHz

- Pin or software controllable DCO on each DSPLL with typical resolution to 1 ppt/step

- TCXO/OCXO reference input determines DSPLL free-run/holdover accuracy and stability

- · Excellent jitter performance

- · Programmable loop bandwidth per DSPLL:

- 1 PPS inputs: 1 mHz and 10 mHz

- · All other inputs: 1 mHz to 4 kHz

- Highly configurable output drivers: LVDS, LVPECL, LVCMOS, HCSL, CML

- · Core voltage:

- VDD: 1.8 V ±5%

- VDDA: 3.3 V ±5%

- · Independent output supply pins: 3.3 V, 2.5 V, or 1.8 V

- · Built-in power supply filtering

- · Status monitoring:

- · LOS, LOL: 1 PPS-750 MHz

- OOF: 8 kHz-750 MHz

- I<sup>2</sup>C Serial Interface

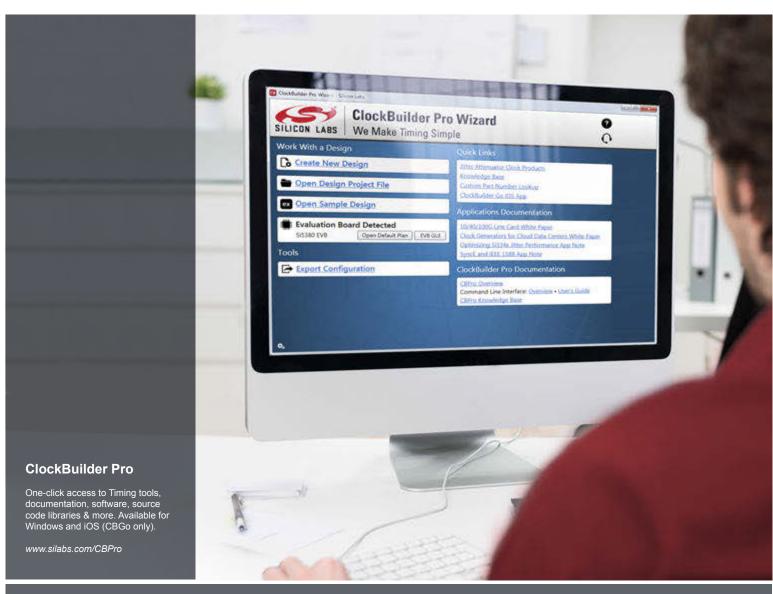

- ClockBuilder<sup>TM</sup> Pro software tool simplifies device configuration

- 5 input, 7 output, 56-pin LGA

- Temperature range: -40 to +85 °C

- · Pb-free, RoHS-6 compliant

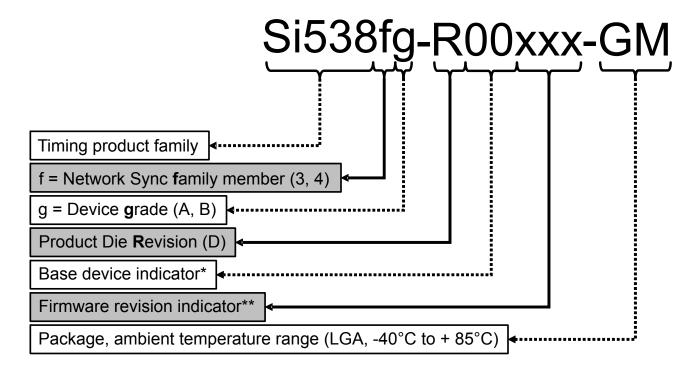

#### 2. Ordering Guide

Table 2.1. Ordering Guide

| Ordering Part Number (OPN) <sup>1,2</sup> | # of DSPLLs | Maximum Out-<br>put Frequency | Package                  | RoHS-6, Pb-<br>Free | Temperature Range |

|-------------------------------------------|-------------|-------------------------------|--------------------------|---------------------|-------------------|

| Si5383A-Dxxxxx-GM                         | 3           | 718.5 MHz                     | 56-Lead 8×8 LGA          | Yes                 | –40 to 85 °C      |

| Si5383B-Dxxxxx-GM                         |             | 350 MHz                       |                          |                     |                   |

| Si5384A-Dxxxxx-GM                         | 1           | 718.5 MHz                     |                          |                     |                   |

| Si5384B-Dxxxxx-GM                         |             | 350 MHz                       |                          |                     |                   |

| Si5383-D-EVB <sup>3</sup>                 | _           | _                             | Evaluation Board         | _                   | _                 |

| SiOCXO1-EVB                               | _           | _                             | OCXO Evaluation<br>Board | _                   | _                 |

#### Notes:

- 1. Add an R at the end of the OPN to denote tape and reel ordering options.

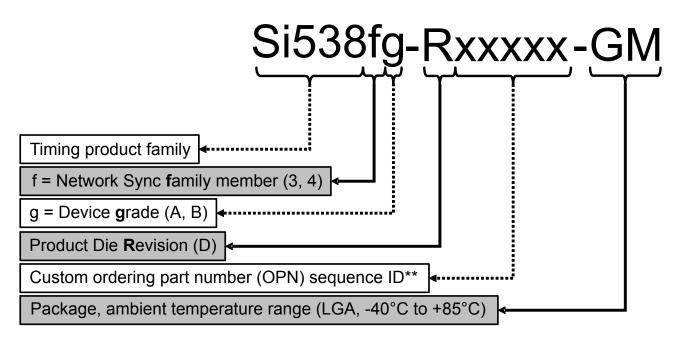

- 2. Custom, factory preprogrammed devices are available as well as unconfigured base devices. See figures below for 5-digit numerical sequence nomenclature.

- 3. The Si5383-D-EVB ships with an SiOCXO1-EVB board included. Additional SiOCXO1-EVB boards may be ordered separately if needed.

#### 2.1 Ordering Part Number Fields

<sup>\*</sup> Firmware is preprogrammed into base devices, but no configuration settings are present in the device

\*\* 3 digits corresponding to the firmware revision preprogrammed into base devices

Figure 2.1. Ordering Guide Part Number Fields for Base Devices

\*\* 5 digits; assigned by ClockBuilder Pro for custom, factory-preprogrammed OPN devices.

The firmware revision for custom OPN devices is determined by ClockBuilder Pro when a custom part number is created.

Figure 2.2. Ordering Guide Part Number Fields for Custom OPN Devices

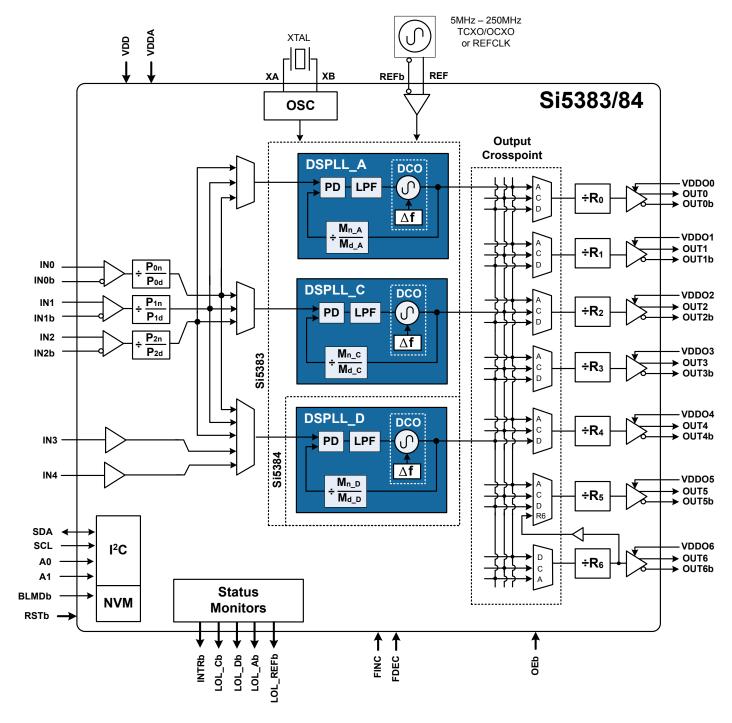

#### 3. Functional Description

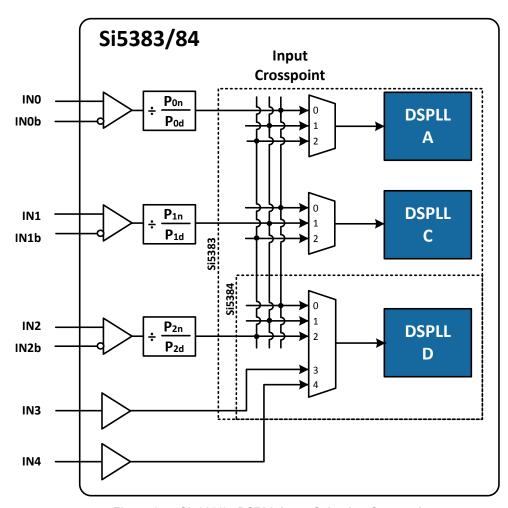

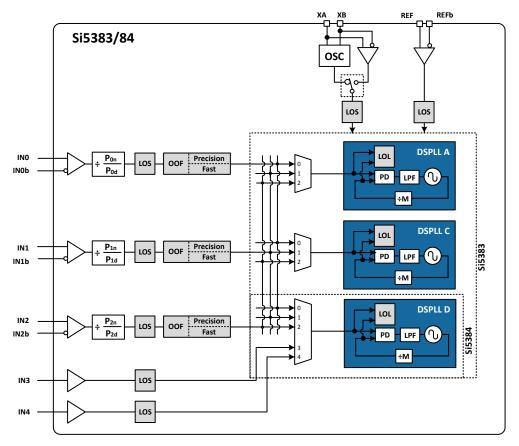

The Si5383 offers three DSPLLs and the Si5384 offers one DSPLL that can be independently configured and controlled through the serial interface. In standard input mode, all DSPLLs support high frequency inputs. DSPLL D can be configured to operate in 1 PPS input mode to lock to a 1 Hz input clock. Regardless of the input mode, any of the DSPLLs can be used to generate any valid output frequency.

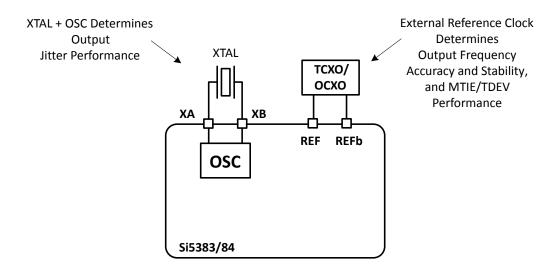

Each of the DSPLLs have locked, free-run, and holdover modes of operation with an optional DCO mode for IEEE 1588 applications. The device requires an external crystal and an external reference (TCXO or OCXO) to operate. The reference input (REF/REFb) determines the frequency accuracy and stability while in free-run and holdover modes. The external crystal completes the internal oscillator circuit (OSC) which is used by the DSPLL for intrinsic jitter performance. There are three main inputs (IN0 - IN2) for synchronizing the DSPLLs. Input selection can be manual or automatically controlled using an internal state machine. Two additional single-ended inputs are available to DSPLL D. Any of the output clocks (OUT0 to OUT6) can be configured to any of the DSPLLs using a flexible crosspoint connection. Output 5 is the only output that can be configured for a 1 Hz output to support 1 PPS.

#### 3.1 Standards Compliance

Each of the DSPLLs meet the applicable requirements of ITU-T G.8262 (SyncE), G.812, G.813, G.8273.2 (T-BC), in addition to Telcordia GR-1244 and GR-253 as shown in the compliance report for standard input mode. The DCO feature enables IEEE1588 (PTP) implementations in addition to hybrid SyncE + IEEE1588 (T-BC).

#### 3.2 Frequency Configuration

The frequency configuration for each of the DSPLLs is programmable through the serial interface and can also be stored in non-volatile memory. The combination of fractional input dividers (Pn/Pd), fractional frequency multiplication (Mn/Md), and integer output division (Rn) allows each of the DSPLLs to lock to any input frequency and generate virtually any output frequency. All divider values for a specific frequency plan are easily determined using the ClockBuilder Pro utility.

#### 3.3 DSPLL Loop Bandwidth in Standard Input Mode

The DSPLL loop bandwidth determines the amount of input clock jitter and wander attenuation. Register configurable DSPLL loop bandwidth settings of 1 mHz to 4 kHz are available for selection for each of the DSPLLs. Since the loop bandwidth is controlled digitally, each of the DSPLLs will always remain stable with less than 0.1 dB of peaking regardless of the loop bandwidth selection.

SONET (Telcordia)

SDH (ITU-T)

SyncE (ITU-T)

Loop Bandwidth

GR-253 Stratum 3E

G.812 Type III

—

0.001 Hz

GR-253 Stratum 3

G.812 Type IV

G.8262 EEC Option 2

< 0.1 Hz</td>

—

G.813 Option 1

G.8262 EEC Option 1

1 - 10 Hz

Table 3.1. Loop Bandwidth Requirements

#### 3.3.1 Fastlock Feature

Selecting a low DSPLL loop bandwidth (e.g. 0.1 Hz) will generally lengthen the lock acquisition time. In standard input mode, the fast-lock feature allows setting a temporary Fastlock Loop Bandwidth that is used during the lock acquisition process. Higher fastlock loop bandwidth settings will enable the DSPLLs to lock faster. Fastlock Loop Bandwidth settings in the range of 100 Hz to 4 kHz are available for selection. Once lock acquisition has completed, the DSPLL's loop bandwidth will automatically revert to the DSPLL Loop Bandwidth setting. The fastlock feature can be enabled or disabled independently for each of the DSPLLs for input frequencies  $\geq$  8 kHz..

#### 3.4 DSPLL Loop Bandwidth in 1 PPS Mode

When operating in 1 PPS input mode, the Si5383/84 offers two choices of loop bandwidth for DSPLL D: 1 mHz or 10 mHz.

#### 3.4.1 Smartlock Feature

When operating in 1 PPS input mode, the Si5383/84 offers the Smartlock feature to achieve fast locking to 1 PPS inputs. The Smartlock feature locks to 1 PPS inputs in two phases. During the first phase, large adjustments are made to eliminate the majority of the frequency and phase error. During the second phase, finer adjustments are made until the PLL is locked. Once the PLL is locked, the DSPLLs loop bandwidth will automatically revert to the DSPLL loop bandwidth setting.

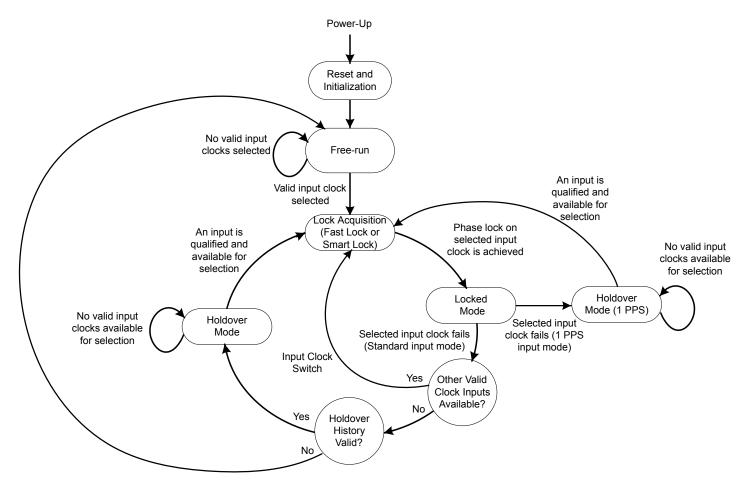

#### 3.5 Modes of Operation

Once initialization is complete, each of the DSPLLs operates independently in one of four modes: Free-run Mode, Lock Acquisition Mode, Locked Mode, or Holdover Mode. A state diagram showing the modes of operation is shown in Figure 3.1 Modes of Operation on page 5. The following sections describe each of these modes in greater detail.

#### 3.5.1 Initialization and Reset

Once power is applied, the device begins an initialization period where it downloads default register values and configuration data from NVM and performs other initialization tasks. Communicating with the device through the serial interface is possible once this initialization period is complete. No clocks will be generated until the initialization is complete. There are two types of resets available. A hard reset is functionally similar to a device power-up. All registers will be restored to the values stored in NVM, and all circuits will be restored to their initial state including the serial interface. A hard reset is initiated using the RSTb pin or by asserting the hard register reset bit. A soft reset bypasses the NVM download. It is simply used to initiate register configuration changes. A hard reset affects all DSPLLs, while a soft reset can either affect all or each DSPLL individually. It is recommended that the device be held in reset during power-up by asserting the RSTb pin. RSTb should be released once all supplies have reached operational levels. The RSTb pin functions as an open-drain output, which drives low during POR. External devices must be configured as open-drain to avoid contention.

Figure 3.1. Modes of Operation

#### 3.5.2 Free-run Mode

Once power is applied to the Si5383/84 and initialization is complete, all three DSPLLs will automatically enter freerun if no clock input is applied. The frequency accuracy of the generated output clocks in freerun mode is entirely dependent on the frequency accuracy of the clock source at the reference inputs (REF/REFb). A TCXO or OCXO is recommended for applications that need frequency accuracy and stability to meet the synchronization standards as shown in the following table:

Table 3.2. Free-run Accuracy for North American and European Synchronization Standards

| SONET (Telcordia) | SDH (ITU-T)    | SyncE (ITU-T)       | Free-run Accuracy |

|-------------------|----------------|---------------------|-------------------|

| GR-253 Stratum 3E | G.812 Type III | _                   | ±4.6 ppm          |

| GR-253 Stratum 3  | G.812 Type IV  | G.8262 EEC Option 2 |                   |

| _                 | G.813 Option 1 | G.8262 EEC Option 1 |                   |

#### 3.5.3 Lock Acquisition Mode

Each of the DSPLLs independently monitors its configured inputs for a valid clock. If at least one valid clock is available for synchronization, a DSPLL will automatically start the lock acquisition process. If the fast lock feature is enabled for inputs  $\geq$  8 kHz, a DSPLL will acquire lock using the Fastlock Loop Bandwidth setting and then transition to the DSPLL Loop Bandwidth setting when lock acquisition is complete. If the input frequency is configured for 1 PPS, the Smartlock mode is used. During lock acquisition the outputs will generate a clock that follows the VCO frequency change as it pulls-in to the input clock frequency.

#### 3.5.4 Locked Mode

Once locked, a DSPLL will generate output clocks that are both frequency and phase locked to their selected input clocks. At this point, any XTAL frequency drift will not affect the output frequency. Each DSPLL has its own LOLb pin and status bit to indicate when lock is achieved. Refer to Section 3.9.6 LOL Detection for more details on the operation of the loss of lock circuit.

#### 3.5.5 Holdover Mode

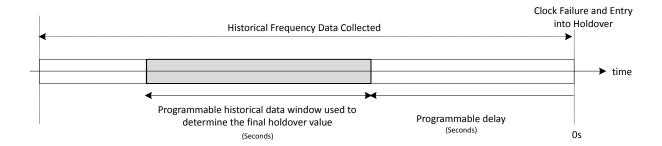

Any of the DSPLLs will automatically enter Holdover Mode when the selected input clock becomes invalid and no other valid input clocks are available for selection. Each DSPLL uses an averaged input clock frequency as its final holdover frequency to minimize the disturbance of the output clock phase and frequency when an input clock suddenly fails. The holdover circuit for each DSPLL stores several seconds of historical frequency data while locked to a valid clock input. The final averaged holdover frequency value is calculated from a programmable window within the stored historical frequency data. Both the window size and delay are programmable as shown in the figure below. The window size determines the amount of holdover frequency averaging. The delay value allows ignoring frequency data that may be corrupt just before the input clock failure.

Figure 3.2. Programmable Holdover Window

When entering holdover, a DSPLL will pull its output clock frequency to the calculated averaged holdover frequency. While in holdover, the output frequency drift is entirely dependent on the external reference clock connected to the REF/REFb pins. When the clock input becomes valid, a DSPLL will automatically exit the holdover mode and re-acquire lock to the new input clock. This process involves pulling the output clock frequencies to achieve frequency and phase lock with the input clock. This pull-in process is glitchless.

In standard input mode, the DSPLL output frequency when exiting holdover can be ramped (recommended). Just before the exit is initiated, the difference between the current holdover frequency and the new desired frequency is measured. Using the calculated difference and a user-selectable ramp rate, the output is linearly ramped to the new frequency. The ramp rate can be 0.2 ppm/s, 40,000 ppm/s, or any of about 40 values in between. The DSPLL loop BW does not limit or affect ramp rate selections (and vice versa). CBPro defaults to ramped exit from holdover. The same ramp rate settings are used for both exit from holdover and ramped input switching. For more information on ramped input switching see Section 3.8.6 Ramped Input Switching in Standard Input Mode.

Note: If ramped holdover exit is not selected, the holdover exit is governed either by (1) the DSPLL loop BW or (2) a user-selectable holdover exit BW.

#### 3.6 Digitally-Controlled Oscillator (DCO) Mode

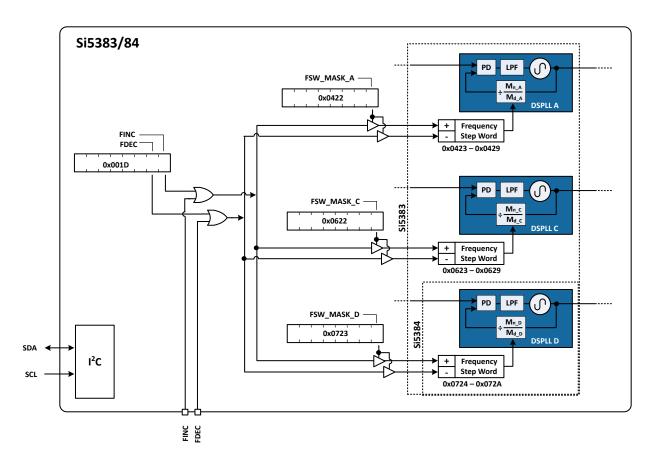

The DSPLLs support a DCO mode where their output frequencies are adjustable in pre-defined steps defined by frequency step words (FSW). The frequency adjustments are controlled through the serial interface or by pin control using frequency increments (FINC) or decrements (FDEC). However due to slower update rates over the I<sup>2</sup>C interface, it is recommended to use pin controls for adjusting the frequency in DCO mode. A FINC will add the frequency step word to the DSPLL output frequency, while a FDEC will decrement it.

The DCO mode is available when the DSPLL is operating in locked mode. The DCO mode is mainly used with standard input mode in IEEE1588 (PTP) applications where a clock needs to be generated based on recovered timestamps. In this case timestamps are recovered by the PHY/MAC. A processor containing servo software controls the DCO to close the timing loop between the master and slave nodes. The processor has the option of using the FINC/FDEC pin controls to update the DCO frequency or by controlling it through the serial interface.

When operating in 1 PPS input mode, an additional enhanced DCO mode is enabled in the holdover state to facilitate DCO steering. This is useful for applications that require Assisted Partial Timing Support (APTS).

#### 3.6.1 Frequency Increment/Decrement Using Pin Controls (FINC, FDEC)

Controlling the output frequency with pin controls is available in standard input mode. This feature involves asserting the FINC or FDEC pins to step (increment or decrement) the DSPLL's output frequency. Both the step size and DSPLL selection (A, C, D) is made through the serial interface by writing to register bits.

Figure 3.3. Controlling the DCO Mode By Pin Control

#### 3.6.2 Frequency Increment/Decrement Using the Serial Interface

Controlling the DSPLL frequency through the serial interface is available. This feature involves asserting the FINC or FDEC bits to activate the frequency change defined by the frequency step word. A set of mask bits selects the DSPLL(s) that is affect by the frequency change.

#### 3.7 External Reference (XA/XB, REF/REFb)

The external crystal at the XA/XB pins determines jitter performance of the output clocks, and the external reference clock at the REF/REFb pins determines the frequency accuracy and stability during free-run or holdover modes, and the MTIE/TDEV performance when the DSPLL is locked. Jitter from the external clock on the REF/REFb pins will have little to no effect on the output jitter performance, depending upon the selected bandwidth. This allows using a lower-cost TCXO/OCXO with a higher phase noise floor or an external reference clock distributed over long PCB traces or across a backplane, without impacting output jitter.

Figure 3.4. External Reference Connections

#### 3.7.1 External Crystal (XA/XB)

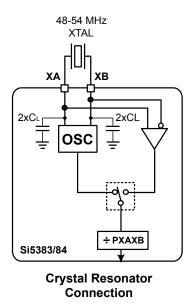

The external crystal (XTAL) is used in combination with the internal oscillator (OSC) to produce an ultra low jitter reference clock for the DSPLLs. The device includes internal XTAL loading capacitors which eliminates the need for external capacitors and also has the benefit of reduced noise coupling from external sources. A crystal in the range of 48 to 54 MHz is recommended for best jitter performance. Although the device includes built-in XTAL load capacitors (CL) of 8 pF, crystals with load capacitances up to 18 pF can also be accommodated. Frequency offsets due to CL mismatch can be adjusted using the frequency adjustment feature which allows frequency adjustments of ±1000 ppm. The Si5383/84 Reference Manual provides additional information on PCB layout recommendations for the crystal to ensure optimum jitter performance. Although it is not recommended, the device can also accommodate an external clock at the XA/XB pins instead of a crystal. Selection between the external crystal or clock is controlled by register configuration. The internal crystal loading capacitors (CL) are disabled in this mode. Refer to Chapter 5. Electrical Specifications for reference clock requirements when using this mode. The Si5383/84 Reference Manual provides additional information on PCB layout recommendations for the crystal to ensure optimum jitter performance.

Figure 3.5. Crystal Resonator Connections

#### 3.7.2 External Reference (REF/REFb)

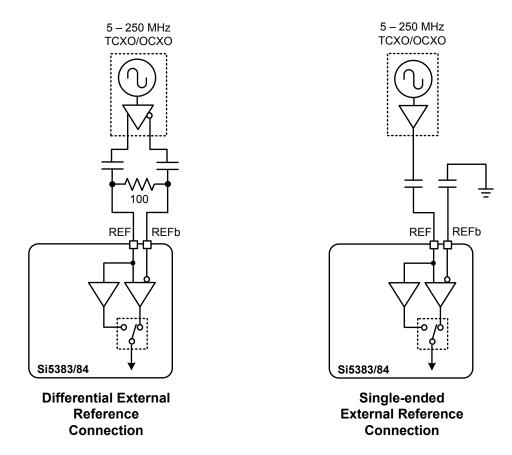

The external reference at the REF/REFb pins is used to determine output frequency accuracy and stability during free-run and holdover modes. This reference is usually from a TCXO or OCXO and can be connected differentially or single-ended as shown in the figure below:

Figure 3.6. External Reference Connections

#### 3.8 Inputs (IN0, IN1, IN2, IN3, IN4)

Inputs IN0, IN1 and IN2 can be used to synchronize any of the DSPLLs. The inputs accept both differential and single-ended clocks. A crosspoint between the inputs and the DSPLLs allows inputs IN0-IN2 to connect to any of the DSPLLs as shown in the figure below. DSPLL D has two additional inputs (IN3-IN4) that are CMOS only inputs. If both IN3 and IN4 are used, they must be the same frequency.

Figure 3.7. Si5383/84 DSPLL Input Selection Crosspoint

#### 3.8.1 Input Selection

Input selection for each of the DSPLLs can be made manually through register control or automatically using an internal state machine.

#### 3.8.2 Manual Input Selection

In manual mode the input selection is made by writing to a register. IN0-IN2 is available to DSPLL A and C, IN0-IN4 is available to DSPLL D. If there is no clock signal on the selected input, the DSPLL will automatically enter holdover mode.

#### 3.8.3 Automatic Input Selection in Standard Input Mode

When configured in this mode, a DSPLL automatically selects a valid input that has the highest configured priority. The priority scheme is independently configurable for each DSPLL and supports revertive or non-revertive selection. All inputs are continuously monitored for loss of signal (LOS) and inputs IN0-IN2 can be monitored for invalid frequency range (OOF). Only inputs that do not assert both the LOS and OOF monitors can be selected for synchronization by the automatic state machine. The DSPLL(s) will enter either holdover or freerun mode if there are no valid inputs available.

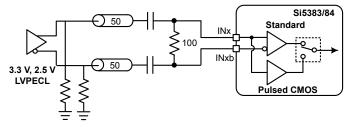

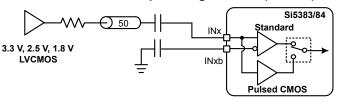

#### 3.8.4 Input Configuration and Terminations

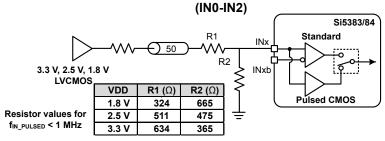

Inputs IN0-IN2 can be configured as differential or single-ended LVCMOS. Inputs IN3-IN4 are single-ended only. The recommended input termination schemes are shown in the figure below. Inputs IN0-IN2 can be disabled and left unconnected when not in use. LVCMOS inputs IN3-IN4 should be externally pulled low when not in use.

# Standard AC-coupled Differential LVDS (IN0-IN2) Si5383/84 Standard Standard INX Pulsed CMOS

#### Standard AC-coupled Differential LVPECL (IN0-IN2)

#### Standard AC-coupled Single-Ended (IN0-IN2)

#### Pulsed CMOS DC-coupled Single-Ended

#### IN3, IN4 - DC-coupled LVCMOS

Figure 3.8. Termination of Differential and LVCMOS Input Signals

#### 3.8.5 Hitless Input Switching in Standard Input Mode

Hitless switching is a feature that prevents a phase offset from propagating to the output when switching between two clock inputs that have a fixed phase relationship. A hitless switch can only occur when the two input frequencies are frequency locked, meaning that they have to be exactly at the same frequency, or at an integer frequency relationship to each other. When hitless switching is enabled, the DSPLL simply absorbs the phase difference between the two input clocks during an input switch. When disabled, the phase difference between the two inputs is propagated to the output at a rate determined by the DSPLL Loop Bandwidth. The hitless switching feature is not available in 1 PPS input mode. Hitless switching can be enabled on a per DSPLL basis.

#### 3.8.6 Ramped Input Switching in Standard Input Mode

When switching between two plesiochronous input clocks (i.e., the frequencies are "almost the same" but not quite), ramped input switching should be enabled to ensure a smooth transition between the two inputs. Ramped input switching avoids frequency transients and overshoot when switching between frequencies and so is the default switching mode in CBPro. The feature should be turned off when switching between input clocks that are always frequency locked (i.e., are always the same exact frequency). The same ramp rate settings are used for both holdover exit and clock switching. For more information on ramped exit from holdover, see Section 3.5.5 Holdover Mode.

#### 3.8.7 Glitchless Input Switching

The DSPLLs have the ability of switching between two input clock frequencies that are up to ±500 ppm apart for standard input mode, and ±10 ppm apart for 1 PPS input mode. The DSPLL will pull-in to the new frequency using the DSPLL Loop Bandwidth or using the Fastlock or Smartlock Loop Bandwidth if it is enabled. The loss of lock (LOL) indicator will assert while the DSPLL is pulling-in to the new clock frequency. There will be no output runt pulses generated at the output during the transition. All clock inputs, including 3 and 4, support glitchless input switching.

#### 3.8.8 Synchronizing to Gapped Input Clocks in Standard Input Mode

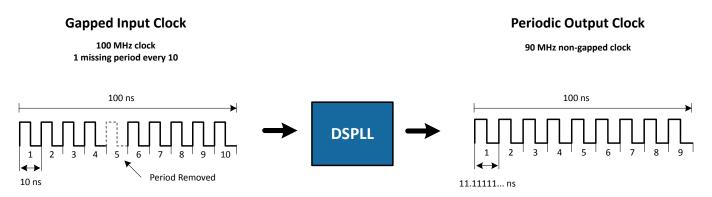

Each of the DSPLLs support locking to an input clock that has missing periods in standard input mode. This is also referred to as a gapped clock. The purpose of gapped clocking is to modulate the frequency of a periodic clock by selectively removing some of its cycles. Gapping a clock severely increases its jitter, so a phase-locked loop with high jitter tolerance and low loop bandwidth is required to produce a low-jitter periodic clock. The resulting output will be a periodic non-gapped clock with an average frequency of the input with its missing cycles. For example, an input clock of 100 MHz with one cycle removed every 10 cycles will result in a 90 MHz periodic non-gapped output clock. This is shown in the figure below:

Figure 3.9. Generating an Averaged Clock Output Frequency from a Gapped Clock Input

A valid gapped clock input must have a minimum frequency of 10 MHz with a maximum of two missing cycles out of every eight. Locking to a gapped clock will not trigger the LOS, OOF, and LOL fault monitors. Clock switching between gapped clocks may violate the hitless switching specification in Table 5.8 Performance Characteristics on page 33 when the switch occurs during a gap in either input clock.

#### 3.9 Fault Monitoring

All input clocks and the reference input (REF/REFb) are monitored for loss of signal (LOS). In addition, inputs IN0-IN2 and REF/REFb are monitored for out-of-frequency (OOF) as shown in the figure below. The reference at the XA/XB pins is also monitored for LOS since it provides a critical reference clock for the DSPLLs. Each of the DSPLLs also has an LOL indicator, which is asserted when synchronization is lost with their selected input clock.

Figure 3.10. Si5383/84 Fault Monitors

#### 3.9.1 Input LOS Detection

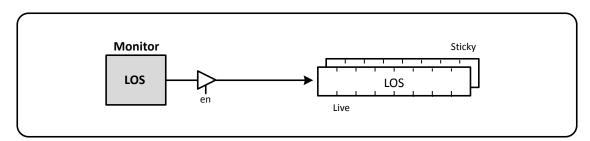

The loss of signal monitor measures the period of each input clock cycle to detect phase irregularities or missing clock edges. Each of the input LOS circuits has its own programmable sensitivity which allows ignoring missing edges or intermittent errors. Loss of signal sensitivity is configurable using the ClockBuilder Pro utility. The LOS status for each of the monitors is accessible by reading a status register. The live LOS register always displays the current LOS state and a sticky register always stays asserted until cleared. An option to disable any of the LOS monitors is also available.

Figure 3.11. LOS Status Indicators

#### 3.9.2 XA/XB LOS Detection

A LOS monitor is available to ensure that the external crystal or reference clock is valid. By default the output clocks are disabled when XAXB\_LOS is detected. This feature can be disabled such that the device will continue to produce output clocks when XAXB\_LOS is detected.

#### 3.9.3 OOF Detection

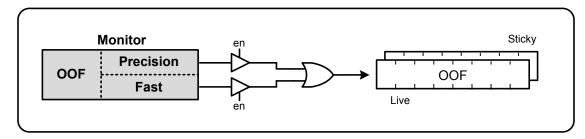

In standard input mode, input clocks IN0, IN1, IN2 are monitored for frequency accuracy with respect to an OOF reference, which it considers as its "0\_ppm" reference. The final OOF status is determined by the combination of both a precise OOF monitor and a fast OOF monitor as shown in the figure below. An option to disable either monitor is also available. The live OOF register always displays the current OOF state and its sticky register bit stays asserted until cleared.

Figure 3.12. OOF Status Indicator

#### 3.9.4 Precision OOF Monitor

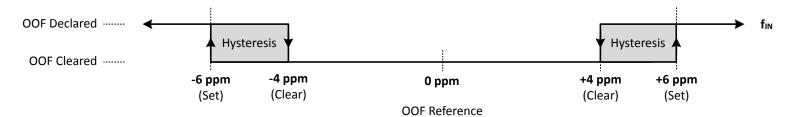

The precision OOF monitor circuit measures the frequency of all input clocks to within ±1/16 ppm accuracy with respect to the selected OOF frequency reference. A valid input clock frequency is one that remains within the OOF frequency range, which is register configurable up to ±500 ppm in steps of 1/16 ppm. A configurable amount of hysteresis is also available to prevent the OOF status from toggling at the failure boundary. An example is shown in the figure below. In this case, the OOF monitor is configured with a valid frequency range of ±6 ppm and with 2 ppm of hysteresis. An option to use one of the input pins (IN0 – IN2) as the 0 ppm OOF reference instead of the REF/REFb pins is available. This option is register-configurable. XA/XB can also be used as the 0 ppm reference.

Figure 3.13. Example of Precise OOF Monitor Assertion and De-assertion Triggers

#### 3.9.5 Fast OOF Monitor

Because the precision OOF monitor needs to provide 1 ppm of frequency measurement accuracy, it must measure the monitored input clock frequencies over a relatively long period of time. This may be too slow to detect an input clock that is quickly ramping in frequency. An additional level of OOF monitoring called the Fast OOF monitor runs in parallel with the precision OOF monitors to quickly detect a ramping input frequency. The Fast OOF monitor asserts OOF on an input clock frequency that has changed by greater than ±4000 ppm.

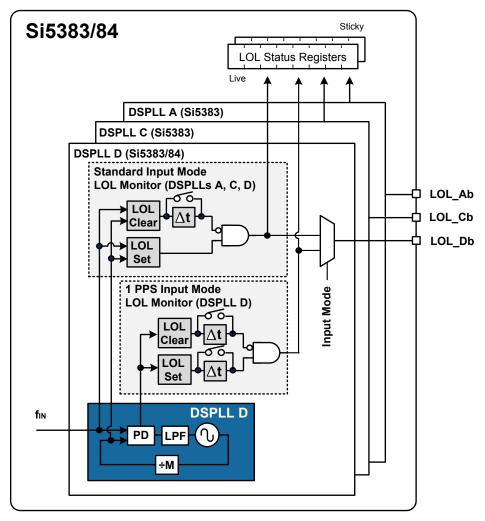

#### 3.9.6 LOL Detection

There is an LOL monitor for each of the DSPLLs. The LOL monitor asserts the LOL register bits when a DSPLL has lost synchronization with its selected input clock. Separate LOL register bits are used to indicate LOL for standard input mode versus 1 PPS mode. There is also a dedicated LOL pin that reflects the loss of lock condition for each of the DSPLLs (LOL\_Ab, LOL\_Cb, LOL\_Db) and also for the reference.

Figure 3.14. Si5383/84 LOL Status Indicators

#### 3.9.6.1 LOL Detection Standard Input Mode

There are two LOL frequency monitors, one that sets the LOL indicator (LOL Set) and another that clears the indicator (LOL Clear). An optional timer is available to delay clearing of the LOL indicator to allow additional time for the DSPLL to completely lock to the input clock. The timer is also useful to prevent the LOL indicator from toggling or chattering as the DSPLL completes lock acquisition. The live LOL register always displays the current LOL state and a sticky register always stays asserted until cleared. The LOLb pin reflects the current state of the LOL monitor.

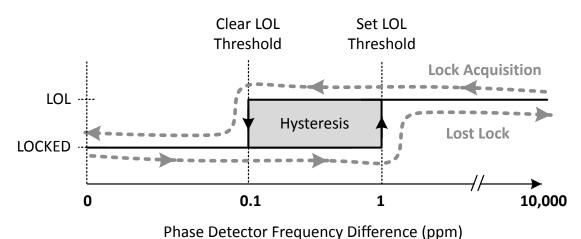

Each of the LOL frequency monitors has adjustable sensitivity, which is register-configurable from 0.1 ppm to 10,000 ppm. Having two separate frequency monitors allows for hysteresis to help prevent chattering of LOL status. An example configuration where LOCK is indicated when there is less than 0.1 ppm frequency difference at the inputs of the phase detector and LOL is indicated when there is more than 1 ppm frequency difference is shown in the figure below.

Figure 3.15. LOL Set and Clear Thresholds

An optional timer is available to delay clearing of the LOL indicator to allow additional time for the DSPLL to completely lock to the input clock. The timer is also useful to prevent the LOL indicator from toggling or chattering as the DSPLL completes lock acquisition. The configurable delay value depends on frequency configuration and loop bandwidth of the DSPLL and is automatically calculated using the ClockBuilderPro utility.

#### 3.9.6.2 LOL Detection in 1 PPS Mode

DSPLL D implements a phase-based LOL detector when operating in PPS mode. Two independent phase error thresholds are included: one for LOL trigger and one for LOL clear. Having two separate phase error thresholds allows for hysteresis to help prevent chattering of the LOL status. An additional level of filtering is provided with trigger and clear counters. These counters represent the number of consecutive clock cycles a threshold must be met before the LOL alarm changes state. These counters prove useful when dealing with transient events, fault conditions, and locking to inputs with noise. For example, the DSPLL may see a large phase error between the time the input signal is lost and the LOS alarm is raised. The user must ensure LOL does not occur during this time to guarantee entry into holdover. This is accomplished by adjusting the LOL trigger counter to a larger value to compensate for this interval.

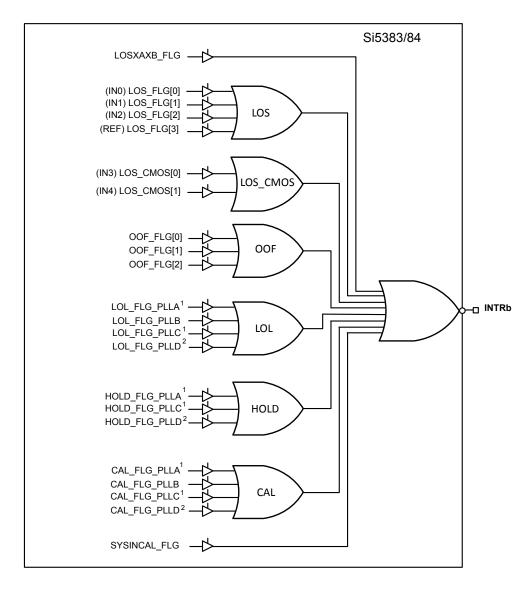

#### 3.9.7 Interrupt Pin (INTRb)

In standard input mode, an interrupt pin (INTRb) indicates a change in state with any of the status indicators for any of the DSPLLs. All status indicators are maskable to prevent assertion of the interrupt pin. The state of the INTRb pin is reset by clearing the sticky status registers.

In 1 PPS input mode, the INTRb pin does not provide status indication for DSPLL D. When operating in this mode, loss of lock for DSPLL D can be monitored using the LOL\_Db pin.

Notes:

- 1. Si5383 only

- 2. Standard input mode only

Figure 3.16. Interrupt Triggers and Masks

#### 3.10 Outputs

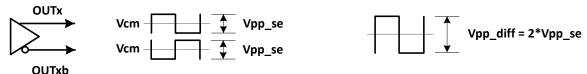

The Si5383/84 supports seven differential output drivers. Each driver has a configurable voltage amplitude and common-mode voltage covering a wide variety of differential signal formats including LVPECL, LVDS, HCSL, and CML. In addition to supporting differential signals, any of the outputs can be configured as single-ended LVCMOS (3.3 V, 2.5 V, or 1.8 V) providing up to 14 single-ended outputs, or a combination of differential and single-ended outputs. LVMOS outputs can also be set for in-phase or complementary mode.

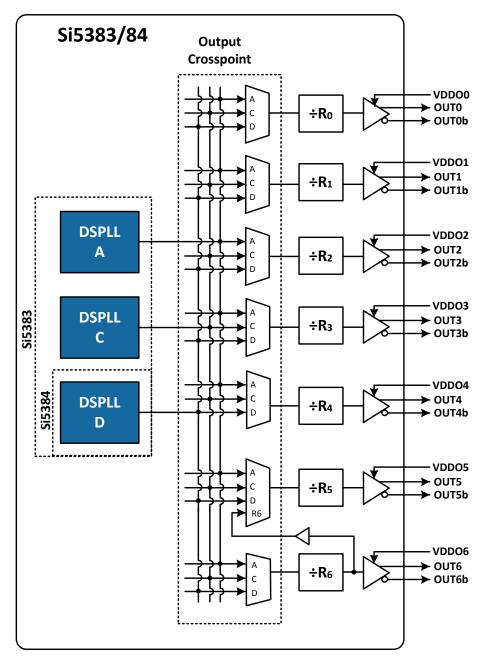

#### 3.10.1 Output Crosspoint

A crosspoint allows any of the output drivers to connect with any of the DSPLLs as shown in the figure below. The crosspoint configuration is programmable and can be stored in NVM so that the desired output configuration is ready at power-up.

Figure 3.17. DSPLL to Output Driver Crosspoint

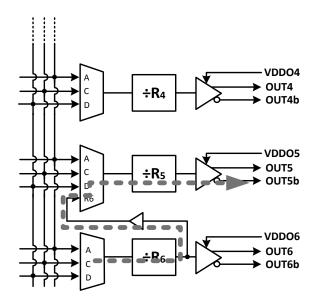

#### 3.10.2 Support For 1 Hz Output

Output 5 of the Si5383/84 can be configured to generate a 1 Hz clock by cascading the R6 and R5 dividers. Output 6 cannot be powered down if Output 5 is used for generating a 1Hz clock. Output 6 is still usable in this case but is limited to a maximum frequency of 33.5 MHz. ClockBuilder Pro automatically determines the optimum configuration when generating a 1 Hz output (1 PPS).

Figure 3.18. Generating a 1 Hz Output using the Si5383/84

#### 3.10.3 Differential Output Terminations

Note: In this document, the terms LVDS and LVPECL refer to driver formats that are compatible with these signaling standards.

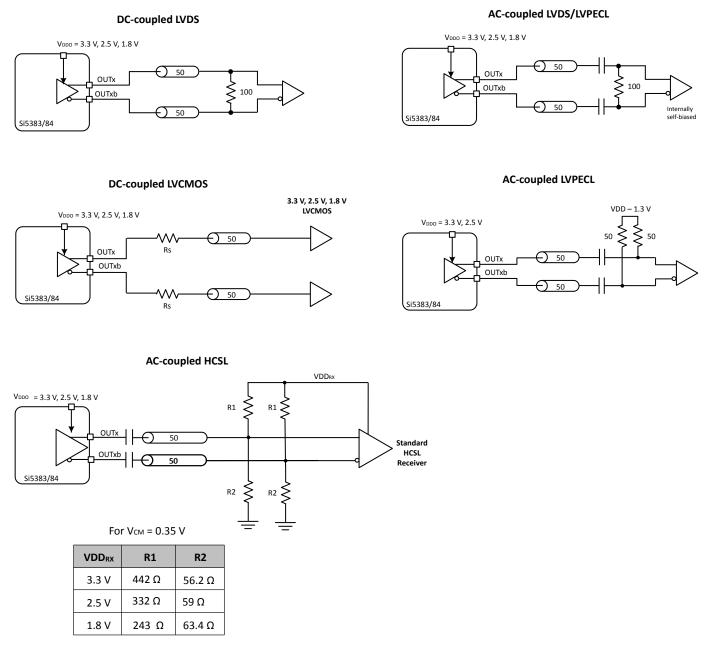

The differential output drivers support both ac-coupled and dc-coupled terminations as shown in the figure below:

Figure 3.19. Supported Differential Output Terminations

#### 3.10.4 Output Signal Format

The differential output amplitude and common-mode voltage are both programmable and compatible with a wide variety of signal formats, including LVDS and LVPECL. In addition to supporting differential signals, any of the outputs can be configured as LVCMOS (3.3 V, 2.5 V, or 1.8 V) drivers providing up to 14 single-ended outputs or a combination of differential and single-ended outputs.

#### 3.10.5 Programmable Common-Mode Voltage For Differential Outputs

The common-mode voltage ( $V_{CM}$ ) for the differential modes is programmable and depends on the voltage available at the output's VDDO pin. Setting the common-mode voltage is useful when dc-coupling the output drivers.

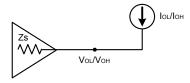

#### 3.10.6 LVCMOS Output Impedance Selection

Each LVCMOS driver has a configurable output impedance to accommodate different trace impedances and drive strengths. A source termination resistor is recommended to help match the selected output impedance to the trace impedance. There are three programmable output impedance selections for each VDDO options as shown in the table below. Note that selecting a lower source impedance may result in higher output power consumption.

Table 3.3. Typical Output Impedance (Z<sub>S</sub>)

| VDDO  | CMOS_DRIVE_Selection |                 |                 |  |  |  |

|-------|----------------------|-----------------|-----------------|--|--|--|

|       | OUTx_CMOS_DRV=1      | OUTx_CMOS_DRV=2 | OUTx_CMOS_DRV=3 |  |  |  |

| 3.3 V | 38 Ω                 | 30 Ω            | 22 Ω            |  |  |  |

| 2.5 V | 43 Ω                 | 35 Ω            | 24 Ω            |  |  |  |

| 1.8 V | _                    | 46 Ω            | 31 Ω            |  |  |  |

#### 3.10.7 LVCMOS Output Signal Swing

The signal swing (V<sub>OL</sub>/V<sub>OH</sub>) of the LVCMOS output drivers is set by the voltage on the VDDO pins. Each output driver has its own VDDO pin allowing a unique output voltage swing for each of the LVCMOS drivers.

#### 3.10.8 LVCMOS Output Polarity

When a driver is configured as an LVCMOS output, it generates a clock signal on both pins (OUTx and OUTxb). By default the clock on the OUTxb pin is generated with the same polarity (in phase) with the clock on the OUTx pin. The polarity of these clocks is configurable, which enables complementary clock generation and/or inverted polarity with respect to other output drivers.

#### 3.10.9 Output Enable/Disable

The OEb pin provides a convenient method of disabling or enabling the output drivers. When the OEb pin is held high, all outputs are disabled. When held low, the outputs are enabled. Outputs in the enabled state can be individually disabled through register control.

#### 3.10.10 Output Disable During LOL

By default, a DSPLL that is out of lock will generate either free-running clocks or generate clocks in holdover mode. In standard input mode, there is an option to disable the outputs when a DSPLL is LOL. This option can be useful to force a downstream PLL into holdover.

#### 3.10.11 Output Disable During XAXB\_LOS

The internal oscillator circuit (OSC) in combination with the external crystal (XTAL) provides a critical function for the operation of the DSPLLs. In the event of a crystal failure the device will assert an XAXB\_LOS alarm. By default all outputs will be disabled during assertion of the XAXB\_LOS alarm. There is an option to leave the outputs enabled during an XAXB\_LOS alarm, but the frequency accuracy and stability will be indeterminate during this fault condition.

#### 3.10.12 Output Driver State When Disabled

The disabled state of an output driver is register configurable as disable low or high.

#### 3.10.13 Synchronous/Asynchronous Output Disable

Outputs can be configured to disable synchronously or asynchronously. In synchronous disable mode the output will wait until a clock period has completed before the driver is disabled. This prevents unwanted runt pulses from occurring when disabling an output. In asynchronous disable mode, the output clock will disable immediately without waiting for the period to complete. By default, ClockBuilder Pro configures outputs for synchronous disable.

#### 3.10.14 Output Divider (R) Synchronization

All the output R dividers are reset to a known state during the power-up initialization period. This ensures consistent and repeatable phase alignment across all output drivers. Resetting the device using the RSTb pin or asserting the hard reset bit will have the same result.

#### 3.10.15 Programmable Phase Offset in 1 PPS Mode

When 1 PPS mode is enabled, the Si5383/84 can be programmed to provide a static phase offset on all outputs generated by DSPLL D. This can be used for compensation of PCB trace delays to achieve accurate system phase alignment for 1 PPS.

#### 3.11 Power Management

Unused inputs, output drivers, and DSPLLs can be powered down when unused. Consult the Si5383/84 Reference Manual and Clock-Builder Pro configuration utility for details.

#### 3.12 In-Circuit Programming

The Si5383/84 is fully configurable using the I<sup>2</sup>C interface. At power-up the device downloads its default register values from internal, flash-based, non-volatile memory (NVM). Application specific default configurations can be written into NVM allowing the device to generate specific clock frequencies at power-up. Firmware updates may also be written into NVM.

The NVM is in-circuit programmable with normal operating power supply voltages using the I<sup>2</sup>C interface. The NVM update process starts by using ClockBuilder Pro to generate a boot record file. Once the boot record has been generated, it is necessary to place the device into bootloader mode via one of the following methods:

- Pin control: Drive the BLMDb pin low prior to negating the RSTb pin

- Register control: Write a boot reset sequence to the device over I<sup>2</sup>C

Once the device has entered bootloader mode, the boot record file can be written to the device over I<sup>2</sup>C. Refer to the *Si5383/84 Reference Manual* for a detailed procedure for writing registers to NVM.

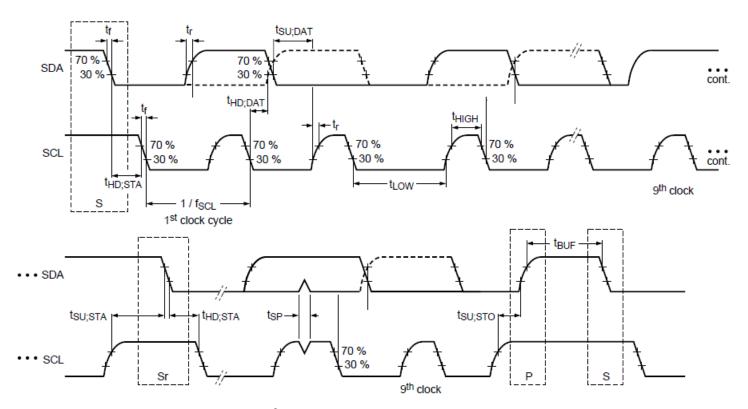

#### 3.13 Serial Interface

Configuration and operation of the Si5383/84 is controlled by reading and writing registers using the I<sup>2</sup>C interface. Communication requires a 3.3 V I/O voltage. The A0 and A1 pins may be used to set the lower two bits of the I<sup>2</sup>C base address if desired. Alternatively, the entire I<sup>2</sup>C base address may be configured using ClockBuilder Pro.

#### 3.14 Custom Factory Preprogrammed Parts

Custom pre-programmed parts can be ordered with a specific configuration written into NVM. A factory pre-programmed part will generate clocks at power-up. Use the ClockBuilder Pro custom part number wizard (www.silabs.com/clockbuilderpro) to quickly and easily request and generate a custom part number for your configuration.

In less than three minutes, you will be able to generate a custom part number with a detailed data sheet addendum matching your design's configuration. Once you receive the confirmation email with the data sheet addendum, simply place an order with your local Silicon Labs sales representative. Samples of your pre-programmed device will typically ship in two weeks.

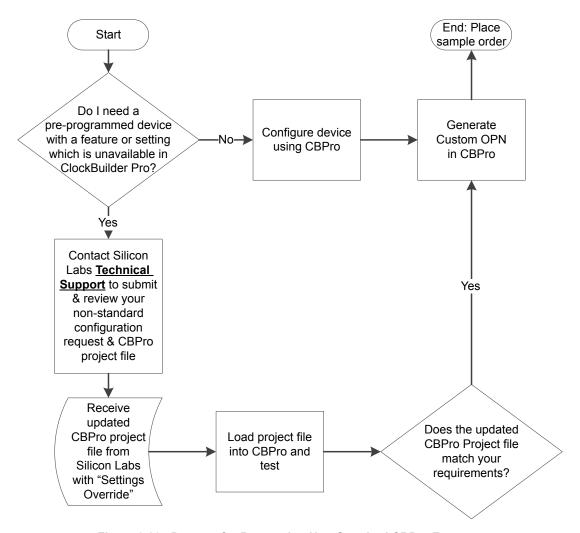

#### 3.15 Enabling Features and/or Configuration Settings Not Available in ClockBuilder Pro for Factory Pre-programmed Devices

As with essentially all modern software utilities, ClockBuilder Pro is continuously updated and enhanced. By registering at www.si-labs.com, you will be notified whenever changes are made and what the impact of those changes are. This update process will ultimately enable ClockBuilder Pro users to access all features and register setting values documented in this data sheet and the Si5383/84 Reference Manual.

However, if you must enable or access a feature or register setting value so that the device starts up with this feature or a register setting, but the feature or register setting is not yet available in CBPro, you must contact a Silicon Labs applications engineer for assistance. One example of this type of feature or custom setting is the customizable output amplitude and common-mode voltages for the clock outputs. After careful review of your project file and requirements, the Silicon Labs applications engineer will email back your CBPro project file with your specific features and register settings enabled using what is referred to as the manual "settings override" feature of CBPro. "Override" settings to match your request(s) will be listed in your design report file. Examples of setting "overrides" in a CBPro design report are shown in the table below:

| Location    | Customer Name   | Туре   | Target      | Dec Value | Hex Value |

|-------------|-----------------|--------|-------------|-----------|-----------|

| 0x0435[0]   | FORCE_HOLD_PLLA | No NVM | N/A         | 1         | 0x1       |

| 0x0B48[4·0] | OOF DIV CLK DIS | User   | OPN and EVB | 31        | 0x1F      |

**Table 3.4. Setting Overrides**

Once you receive the updated design file, simply open it in CBPro. The device will begin operation after startup with the values in the NVM file. The flowchart for this process is shown in the figure below:

Figure 3.20. Process for Requesting Non-Standard CBPro Features

#### 4. Register Map

Registers in the Si5383/84 require an I<sup>2</sup>C command sequence to enable the reading and writing. Once the I<sup>2</sup>C command sequences have been sent, it is necessary for the host to poll the status bits to indicate that the read or write command is complete. For read commands, data is available once the status bit indicates the command is complete. Refer to the Si5383/84 Reference Manual for a complete list of register descriptions and settings.

#### 5. Electrical Specifications

**Table 5.1. Recommended Operating Conditions**

| Parameter                    | Symbol            | Min  | Тур  | Max  | Unit |

|------------------------------|-------------------|------|------|------|------|

| Ambient Temperature          | T <sub>A</sub>    | -40  | 25   | 85   | °C   |

| Junction Temperature         | TJ <sub>MAX</sub> | _    | _    | 125  | °C   |

| Core Supply Voltage          | $V_{DD}$          | 1.71 | 1.80 | 1.89 | V    |

|                              | $V_{DDA}$         | 3.14 | 3.30 | 3.47 | V    |

| Output Driver Supply Voltage | $V_{DDO}$         | 3.14 | 3.30 | 3.47 | V    |

|                              |                   | 2.37 | 2.50 | 2.62 | V    |

|                              |                   | 1.71 | 1.80 | 1.89 | V    |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

Table 5.2. DC Characteristics

$(VDD = 1.8 \text{ V} \pm 5\%, VDDA = 3.3 \text{ V} \pm 5\%, VDDO = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, \text{ TA} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                            | Symbol                                     | Test Condition                                   | Min  | Тур  | Max   | Unit |

|--------------------------------------|--------------------------------------------|--------------------------------------------------|------|------|-------|------|

| Core Supply Current                  | I <sub>DD</sub>                            | Si5383, 1 PPS Input Mode <sup>1</sup>            | _    | 245  | 390   | mA   |

|                                      |                                            | Si5383, Standard Input Mode <sup>2</sup>         | _    | 240  | 380   | mA   |

|                                      |                                            | Si5384, 1 PPS Input Mode <sup>1</sup>            | _    | 165  | 390   | mA   |

|                                      | I <sub>DDA</sub>                           | Si5383, 1 PPS Input Mode <sup>1</sup>            | _    | 160  | 190   | mA   |

|                                      |                                            | Si5383, Standard Input Mode <sup>2</sup>         | _    | 160  | 190   | mA   |

|                                      |                                            | Si5384, 1 PPS Input Mode <sup>1</sup>            | _    | 155  | 180   | mA   |

| Output Buffer Supply Current         | I <sub>DDOx</sub>                          | LVPECL Output <sup>3</sup> @ 156.25 MHz          | _    | 22   | 22 26 | mA   |

|                                      |                                            | LVDS Output <sup>3</sup> @ 156.25 MHz            | _    | 15   | 18    | mA   |

|                                      |                                            | 3.3 V LVCMOS <sup>4</sup><br>Output @ 156.25 MHz | _    | 22   | 30    | mA   |

|                                      |                                            | 2.5 V LVCMOS <sup>4</sup><br>Output @ 156.25 MHz | _    | 18   | 23    | mA   |

|                                      |                                            | 1.8 V LVCMOS <sup>4</sup><br>Output @ 156.25 MHz | _    | 12   | 16    | mA   |

| Total Power Dissipation <sup>5</sup> | P <sub>d</sub>                             | Si5383, 1 PPS Input Mode <sup>1</sup>            | _    | 1265 | 1620  | mW   |

|                                      | Si5383, Standard Input Mode <sup>2</sup> — | _                                                | 1255 | 1610 | mW    |      |

|                                      |                                            | Si5384, 1 PPS Input Mode <sup>1</sup>            | _    | 1100 | 1410  | mW   |

| Analog Supply Voltage Ramp<br>Time   | t <sub>RMP_VDDA</sub>                      | Time to V <sub>DDA</sub> > 2.2 V                 | 10   | _    | _     | μs   |

| Parai | meter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-------|-------|--------|----------------|-----|-----|-----|------|

|       |       |        |                |     |     |     |      |

#### Notes:

- 1. Test configuration: 7 x 2.5 V LVDS outputs enabled @156.25 MHz. 1 PPS input enabled on DSPLL D. Excludes power in termination resistors.

- 2. Test configuration: 7 x 2.5 V LVDS outputs enabled @156.25 MHz. 1 PPS input not enabled. Excludes power in termination resistors.

- 3. Differential outputs terminated into an AC coupled 100  $\Omega$  load.

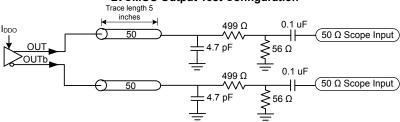

- 4. LVCMOS outputs measured into a 5-inch 50 Ω PCB trace with 5 pF load. The LVCMOS outputs were set to OUTx\_CMOS\_DRV= 3, which is the strongest driver setting. Refer to the *Si5383/84 Reference Manual* for more details on register settings.

- 5. Detailed power consumption for any configuration can be estimated using ClockBuilderPro when an evaluation board (EVB) is not available. All EVBs support detailed current measurements for any configuration.

**Table 5.3. Input Clock Specifications**

(VDD = 1.8 V  $\pm 5\%$ , VDDA = 3.3 V  $\pm 5\%$ , TA = -40 to 85 °C)

| Parameter                  | Symbol                         | Test Condition                                                 | Min                  | Тур        | Max                  | Unit    |

|----------------------------|--------------------------------|----------------------------------------------------------------|----------------------|------------|----------------------|---------|

| Standard Input Buffer with | Differential or Sing           | le-Ended/LVCMOS Configuration                                  | - AC-Coupled         | (IN0, IN1, | IN2, REF)            |         |

| Input Frequency Range      | f <sub>IN</sub>                | Differential                                                   | 0.008                | _          | 750                  | MHz     |

|                            |                                | Single-ended/LVCMOS                                            | 0.008                | _          | 250                  |         |

|                            |                                | REF                                                            | 5                    | _          | 250                  |         |

| Voltage Swing <sup>1</sup> | V <sub>IN</sub>                | Differential AC-coupled f <sub>IN</sub> < 250 MHz              | 100                  | _          | 1800                 | mVpp_se |

|                            |                                | Differential AC-coupled<br>250 MHz < f <sub>IN</sub> < 750 MHz | 225                  | _          | 1800                 | mVpp_se |

|                            |                                | Single-Ended AC-coupled f <sub>IN</sub> < 250 MHz              | 100                  | _          | 3600                 | mVpp_se |

| Slew Rate <sup>2,3</sup>   | SR                             |                                                                | 400                  | _          | _                    | V/µs    |

| Duty Cycle                 | DC                             |                                                                | 40                   | _          | 60                   | %       |

| Input Capacitance          | C <sub>IN</sub>                |                                                                | _                    | 0.3        | _                    | pF      |

| Input Resistance           | R <sub>IN</sub>                | Differential                                                   | _                    | 16         | _                    | kΩ      |

|                            |                                | Single-ended/LVCMOS                                            | _                    | 8          | _                    |         |

| Pulsed CMOS - DC-coupled   | i (IN0, IN1, IN2) <sup>4</sup> |                                                                |                      |            | -                    |         |

| Input Frequency            | f <sub>IN</sub> _              | Standard Mode                                                  | 0.008                | _          | 250                  | MHz     |

| . ,                        | PULSED                         | 1 PPS Mode                                                     | _                    | 1          | _                    | Hz      |

| Input Voltage              | V <sub>IL</sub>                |                                                                | _                    | _          | 0.4                  | V       |

|                            | V <sub>IH</sub>                |                                                                | 0.8                  | _          | _                    | V       |

| Slew Rate <sup>2,3</sup>   | SR                             |                                                                | 400                  | _          | _                    | V/µs    |

| Minimum Pulse Width        | PW                             | Standard Mode                                                  | 1.6                  | _          | _                    | ns      |

|                            |                                | 1 PPS Mode                                                     | 10                   | _          | _                    | us      |

| Input Resistance           | R <sub>IN</sub>                |                                                                | _                    | 8          | _                    | kΩ      |

| LVCMOS - DC Coupled (IN3   | 3, IN4)                        |                                                                |                      |            |                      |         |

| Input Frequency            | f <sub>IN_PULSE</sub>          | Standard Mode                                                  | 0.008                | _          | 2.048                | MHz     |

|                            | D                              | 1 PPS Mode                                                     | _                    | 1          | _                    | Hz      |

| Input Voltage              | V <sub>IL</sub>                |                                                                | _                    | _          | 0.3xV <sub>DDA</sub> | V       |

|                            | V <sub>IH</sub>                |                                                                | 0.7xV <sub>DDA</sub> | _          | _                    | V       |

| Minimum Pulse Width        | PW                             | Standard Mode, Pulse Input                                     | 50                   | _          | _                    | ns      |

| William Fulse Width        |                                | 1 PPS Mode, Pulse Input                                        | 10                   | _          | _                    | us      |

| Input Resistance           | R <sub>IN</sub>                |                                                                | _                    | 20         | _                    | kΩ      |

| Parameter                | Symbol               | Test Condition                                           | Min   | Тур | Max   | Unit      |

|--------------------------|----------------------|----------------------------------------------------------|-------|-----|-------|-----------|

| XA/XB Frequency          | f <sub>IN_XAXB</sub> | Full operating range. Jitter performance may be reduced. | 24.97 | _   | 54.06 | MHz       |

|                          |                      | Frequency range for best output jitter performance.      | 48    | _   | 54    | MHz       |

| Input Voltage Swing      | V <sub>IN_SE</sub>   | Single-ended                                             | 365   | _   | 2000  | mVpp_se   |

|                          | V <sub>IN_DIFF</sub> | Differential                                             | 365   | _   | 2500  | mVpp_diff |

| Slew rate <sup>2,3</sup> | SR                   | Imposed for best jitter performance                      | 400   | _   | _     | V/µs      |

| Input Duty Cycle         | DC                   |                                                          | 40    | _   | 60    | %         |

#### Note:

1. Voltage swing is specified as single-ended mVpp.

- 2. Imposed for jitter performance.

- 3. Rise and fall times can be estimated using the following simplified equation:  $tr/tf_{80-20} = ((0.8 0.2) \times V_{IN\_Vpp\_se}) / SR$ .

- 4. Pulsed CMOS mode is intended primarily for single-ended LVCMOS input clocks < 1 MHz, which must be dc-coupled because they have a duty cycle significantly less than 50%. A typical application example is a low frequency video frame sync pulse. Since the input thresholds (V<sub>IL</sub>, V<sub>IH</sub>) of this buffer are non-standard (0.4 and 0.8 V, respectively), refer to the input attenuator circuit for DC-coupled Pulsed LVCMOS in the *Si5383/84 Reference Manual*. Otherwise, for standard LVCMOS input clocks, use the Standard AC-coupled, Single-ended input mode.

Table 5.4. Control Input Pin Specifications

$(VDD = 1.8 V \pm 5\%, VDDA = 3.3 V \pm 5\%, TA = -40 to 85 °C)$

| Parameter                       | Symbol             | Test Condition | Min                       | Тур | Max                       | Unit |

|---------------------------------|--------------------|----------------|---------------------------|-----|---------------------------|------|

| Si5383/84 Control Input Pins (I | FINC, FDEC, OEb)   |                | <u> </u>                  |     |                           |      |

| Input Voltage                   | V <sub>IL</sub>    |                | _                         | _   | 0.3 x<br>V <sub>DDA</sub> | V    |

|                                 | V <sub>IH</sub>    |                | 0.7 x<br>V <sub>DDA</sub> | _   | _                         | V    |

| Input Capacitance               | C <sub>IN</sub>    |                | _                         | 2   | _                         | pF   |

| Input Resistance                | RL                 |                | _                         | 20  | _                         | kΩ   |

| Minimum Pulse Width             | PW                 | FINC, FDEC     | 100                       | _   | _                         | ns   |

| Update Rate                     | F <sub>UR</sub>    | FINC, FDEC     | _                         | _   | 1                         | MHz  |

| Si5383/84 Control Input Pin (S  | CL, SDA, A1, A0, B | LMDb, RSTb)    | <u> </u>                  |     |                           | I    |

| Input Voltage                   | V <sub>IL</sub>    |                | _                         | _   | 0.3 x<br>V <sub>DDA</sub> | V    |

|                                 | V <sub>IH</sub>    |                | 0.7 x<br>V <sub>DDA</sub> | _   | _                         | V    |

| Input Capacitance               | C <sub>IN</sub>    |                |                           | 7   | _                         | pF   |

| Minimum Reset Pulse Width       | PW                 |                | 15                        | _   | _                         | μs   |

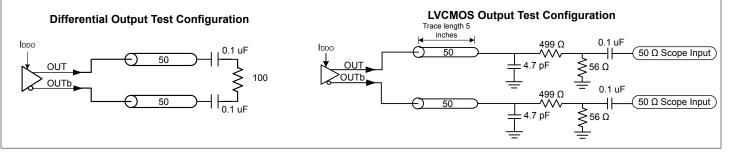

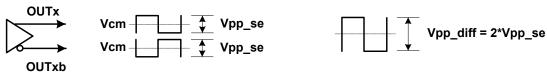

#### **Table 5.5. Differential Clock Output Specifications**

$(VDD = 1.8 \text{ V} \pm 5\%, VDDA = 3.3 \text{ V} \pm 5\%, VDDO = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, \text{ TA} = -40 \text{ to } 85 \text{ °C})$

| Parameter                                    | Symbol                                                      | Test Condition                                  | Min              | Тур  | Max   | Unit |         |

|----------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|------------------|------|-------|------|---------|

| Output Frequency                             | f <sub>OUT</sub>                                            | Standard input mode                             | 0.0001           | _    | 718.5 | MHz  |         |

|                                              |                                                             | DSPLL D in 1 PPS mode                           | 0.0001           | _    | 685   | MHz  |         |

|                                              | f <sub>OUT1Hz</sub> 1 PPS signal only available on Output 5 |                                                 | on               | _    | 1     | _    | Hz      |

| Duty Cycle                                   | DC                                                          | f <sub>OUT</sub> < 400 MHz                      | 48               | _    | 52    | %    |         |

|                                              |                                                             | 400 MHz < f <sub>OUT</sub> < 712.5 MHz          |                  | 45   | _     | 55   | %       |

| Output-Output Skew                           | T <sub>SK</sub>                                             | Outputs on same DSPLI<br>(measured at 712.5 MHz |                  | _    | _     | 65   | ps      |

| OUT-OUTb Skew                                | T <sub>SK_OUT</sub>                                         | Measured from the positive to r output pins     | _                | 0    | 50    | ps   |         |

| Output Voltage Amplitude <sup>1</sup>        | V <sub>OUT</sub>                                            | V <sub>DDO</sub> = 3.3 V, 2.5 V, or 1.8 V       | LVDS             | 350  | 430   | 510  | mVpp_se |

|                                              |                                                             | V <sub>DDO</sub> = 3.3 V, or 2.5 V              | LVPECL           | 640  | 750   | 900  |         |

| Common-Mode Voltage <sup>1</sup>             | V <sub>CM</sub>                                             | V <sub>DDO</sub> = 3.3 V                        | LVDS             | 1.10 | 1.20  | 1.30 | V       |

|                                              |                                                             |                                                 | LVPECL           | 1.90 | 2.00  | 2.10 |         |

|                                              |                                                             | V <sub>DDO</sub> = 2.5 V                        | LVPECL<br>, LVDS | 1.10 | 1.20  | 1.30 |         |

|                                              |                                                             | V <sub>DDO</sub> = 1.8 V                        | sub-<br>LVDS     | 0.80 | 0.90  | 1.00 |         |

| Rise and Fall Times (20% to 80%)             | t <sub>R</sub> /t <sub>F</sub>                              |                                                 |                  | _    | 100   | 150  | ps      |

| Differential Output Impedance                | Z <sub>O</sub>                                              |                                                 |                  | _    | 100   | _    | Ω       |

| Power Supply Noise<br>Rejection <sup>2</sup> | PSRR                                                        | 10 kHz sinusoidal noise                         |                  | _    | -99   | _    | dBc     |

|                                              |                                                             | 100 kHz sinusoidal noise                        |                  | _    | -96   | _    |         |

|                                              |                                                             | 500 kHz sinusoidal noise                        |                  | _    | -94   |      |         |

|                                              |                                                             | 1 MHz sinusoidal noise                          | _                | -93  | _     |      |         |

| Output-output Crosstalk <sup>3</sup>         | XTALK                                                       | Measured spur from adjacent of                  | _                | -86  | _     | dBc  |         |

#### Notes:

- 1. Output amplitude and common-mode voltage are programmable through register settings and can be stored in NVM. Each output driver can be programmed independently. The maximum LVDS single-ended amplitude can be up to 110 mV higher than the TIA/ EIA-644 maximum. Refer to the Si5383/84 Family Reference Manual for more suggested output settings. Not all combinations of voltage amplitude and common-mode voltages settings are possible.

- 2. Measured for 156.25 MHz carrier frequency. 100mVpp of sinewave noise added to VDDO = 3.3V and noise spur amplitude measured.