Part number:

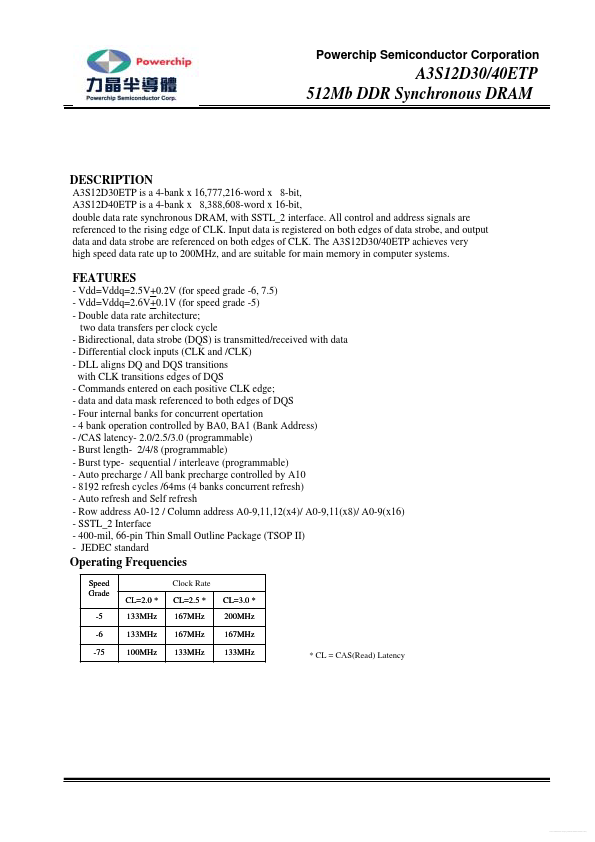

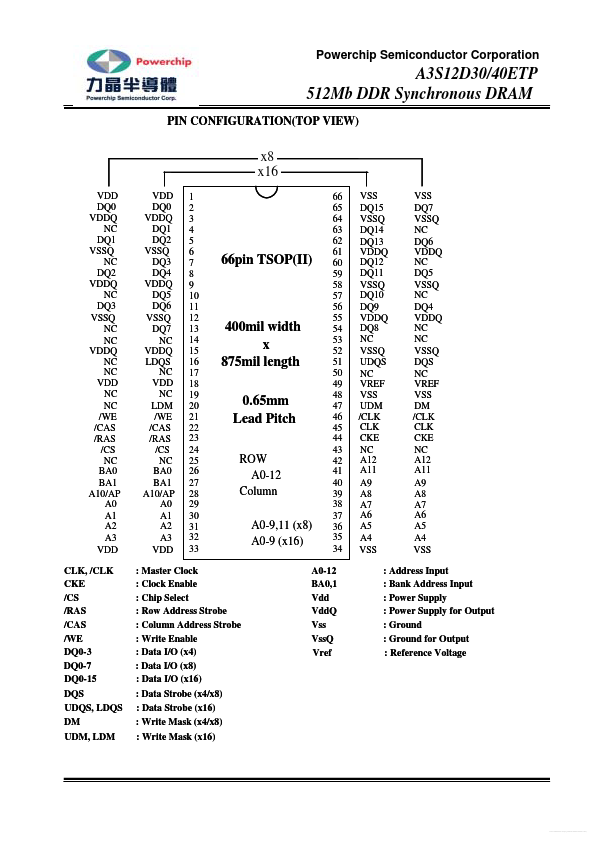

A3S12D40ETP, A3S12D30ETP

Manufacturer:

Powerchip

File Size:

2.10 MB

Description:

512mb ddr sdram.

This datasheet PDF includes multiple part numbers: A3S12D40ETP, A3S12D30ETP.

Please refer to the document for exact specifications by model.