PLL520-08

PLL520-08 is (PLL520-0x) Low Phase Noise VCXO manufactured by PhaseLink Corporation.

- Part of the PLL520-05 comparator family.

- Part of the PLL520-05 comparator family.

PLL520-05/-06/-07/-08/-09

..

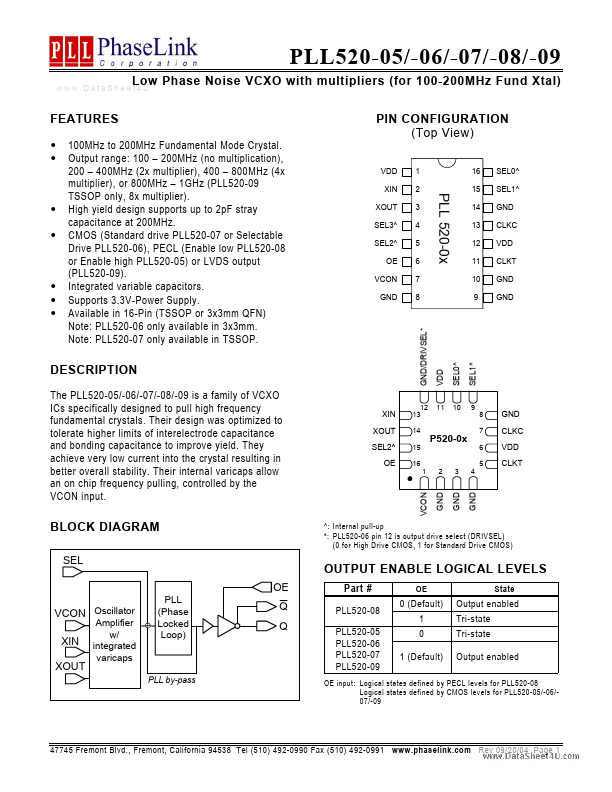

Low Phase Noise VCXO with multipliers (for 100-200MHz Fund Xtal) PIN CONFIGURATION (Top View)

VDD XIN XOUT SEL3^ SEL2^ OE VCON GND 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 SEL0^ SEL1^ GND CLKC VDD CLKT GND GND

Features

- - 100MHz to 200MHz Fundamental Mode Crystal. Output range: 100

- 200MHz (no multiplication), 200

- 400MHz (2x multiplier), 400

- 800MHz (4x multiplier), or 800MHz

- 1GHz (PLL520-09 TSSOP only, 8x multiplier). High yield design supports up to 2pF stray capacitance at 200MHz. CMOS (Standard drive PLL520-07 or Selectable Drive PLL520-06), PECL (Enable low PLL520-08 or Enable high PLL520-05) or LVDS output (PLL520-09). Integrated...