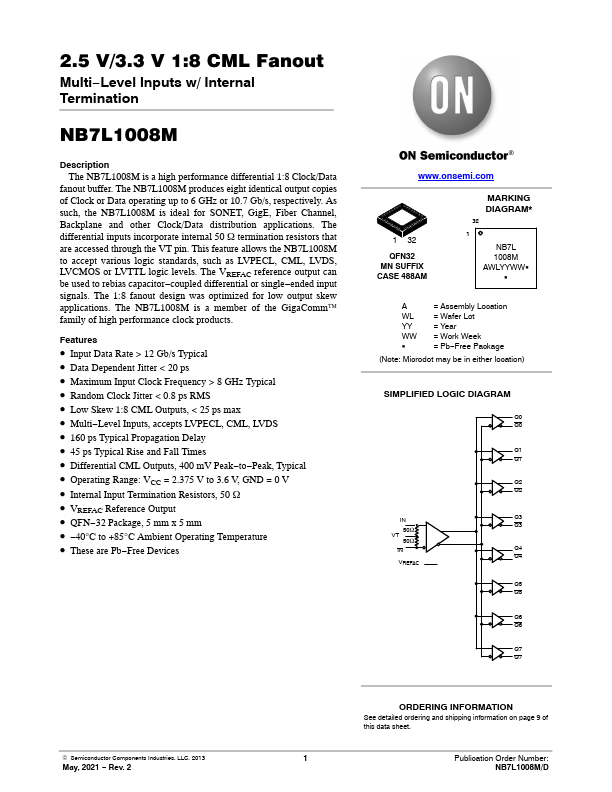

NB7L1008M Overview

The NB7L1008M is a high performance differential 1:8 Clock/Data fanout buffer. The NB7L1008M produces eight identical output copies of Clock or Data operating up to 6 GHz or 10.7 Gb/s, respectively. As such, the NB7L1008M is ideal for SONET, GigE, Fiber Channel, Backplane and other Clock/Data distribution applications.

NB7L1008M Key Features

- Input Data Rate > 12 Gb/s Typical

- Data Dependent Jitter < 20 ps

- Maximum Input Clock Frequency > 8 GHz Typical

- Random Clock Jitter < 0.8 ps RMS

- Low Skew 1:8 CML Outputs, < 25 ps max

- Multi-Level Inputs, accepts LVPECL, CML, LVDS

- 160 ps Typical Propagation Delay

- 45 ps Typical Rise and Fall Times

- Differential CML Outputs, 400 mV Peak-to-Peak, Typical

- Operating Range: VCC = 2.375 V to 3.6 V, GND = 0 V