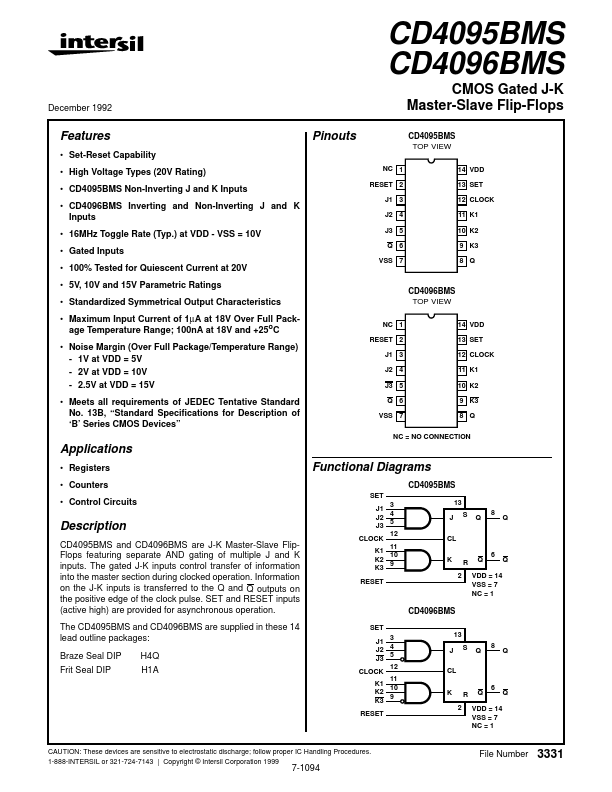

CD4095BMS Overview

The gated J-K inputs control transfer of information into the master section during clocked operation. Information on the J-K inputs is transferred to the Q and Q outputs on the positive edge of the clock pulse. SET and RESET inputs (active high) are provided for asynchronous operation.

CD4095BMS Key Features

- Set-Reset Capability

- High Voltage Types (20V Rating)

- CD4095BMS Non-Inverting J and K Inputs

- CD4096BMS Inverting and Non-Inverting J and K Inputs

- 16MHz Toggle Rate (Typ.) at VDD

- VSS = 10V

- Gated Inputs

- 100% Tested for Quiescent Current at 20V

- 5V, 10V and 15V Parametric Ratings

- Standardized Symmetrical Output Characteristics