ICS8602

Overview

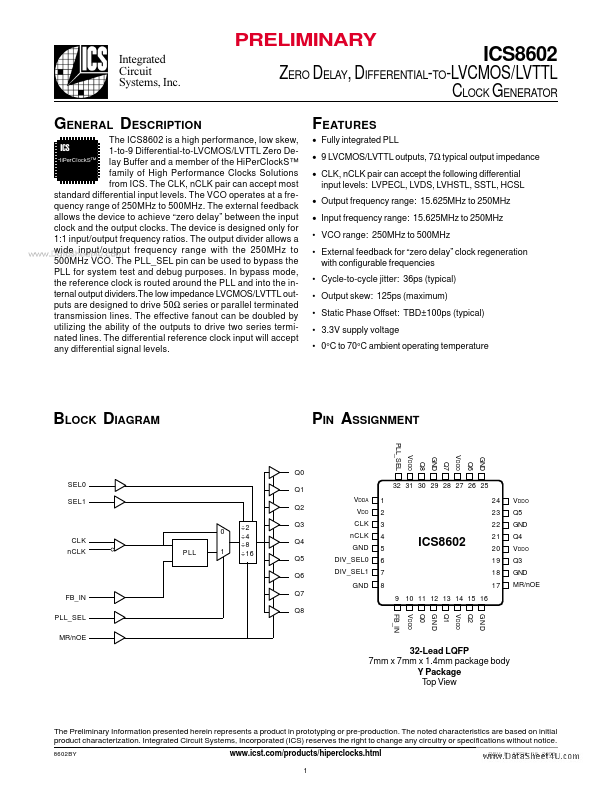

The ICS8602 is a high performance, low skew, ,&6 1-to-9 Differential-to-LVCMOS/LVTTL Zero DeHiPerClockS™ lay Buffer and a member of the HiPerClockS™ family of High Performance Clocks Solutions from ICS. The CLK, nCLK pair can accept most standard differential input levels.

- Fully integrated PLL

- 9 LVCMOS/LVTTL outputs, 7Ω typical output impedance

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Output frequency range: 15.625MHz to 250MHz

- Input frequency range: 15.625MHz to 250MHz

- VCO range: 250MHz to 500MHz

- External feedback for “zero delay” clock regeneration with configurable frequencies

- Cycle-to-cycle jitter: 36ps (typical)

- Output skew: 125ps (maximum)

- Static Phase Offset: TBD±100ps (typical)