CY7C1363C

Overview

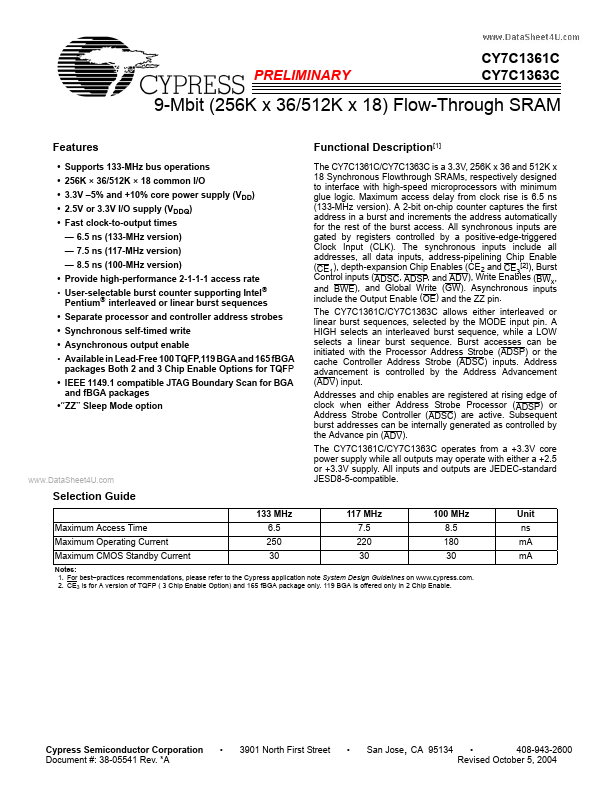

- Supports 133-MHz bus operations

- 256K × 36/512K × 18 common I/O

- 3.3V -5% and +10% core power supply (VDD)

- 2.5V or 3.3V I/O supply (VDDQ)

- Fast clock-to-output times - 6.5 ns (133-MHz version) - 7.5 ns (117-MHz version) - 8.5 ns (100-MHz version)

- Provide high-performance 2-1-1-1 access rate

- User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences

- Separate processor and controller address strobes

- Synchronous self-timed write

- Asynchronous output enable