SN75LVDS83A Key Features

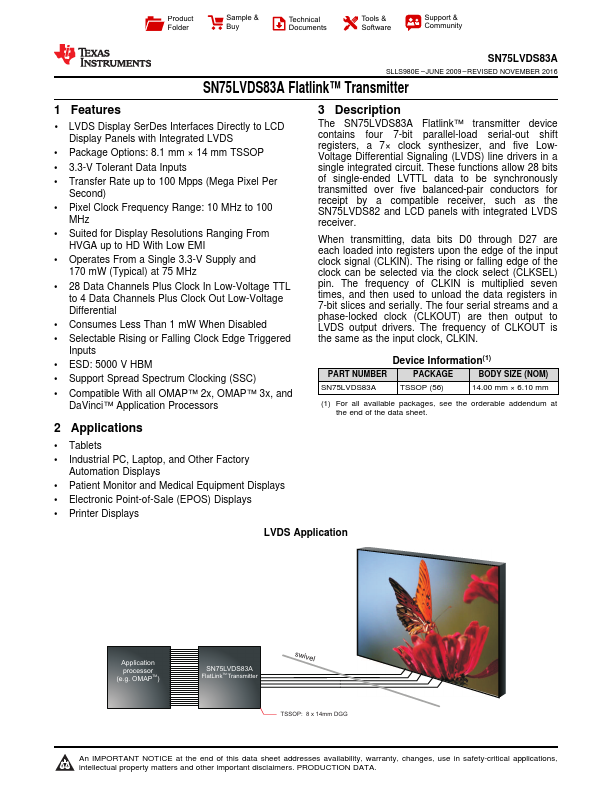

- 1 LVDS Display SerDes Interfaces Directly to LCD Display Panels with Integrated LVDS

- Package Options: 8.1 mm × 14 mm TSSOP

- 3.3-V Tolerant Data Inputs

- Pixel Clock Frequency Range: 10 MHz to 100

- Suited for Display Resolutions Ranging From

- Operates From a Single 3.3-V Supply and

- 28 Data Channels Plus Clock In Low-Voltage TTL

- Consumes Less Than 1 mW When Disabled

- Selectable Rising or Falling Clock Edge Triggered Inputs

- ESD: 5000 V HBM