ST2318

DESCRIPTION

ST2318 is the N-Channel logic enhancement mode power field effect transistor are produced using high cell density, DMOS trench technology.This high density process is especially tailored to minimize on-state resistance.These devices are particularly suited for low voltage application such as cellular phone and notebook puter power management, other battery powered circuits, and low in-line power loss are needed in a very small outline surface mount package.

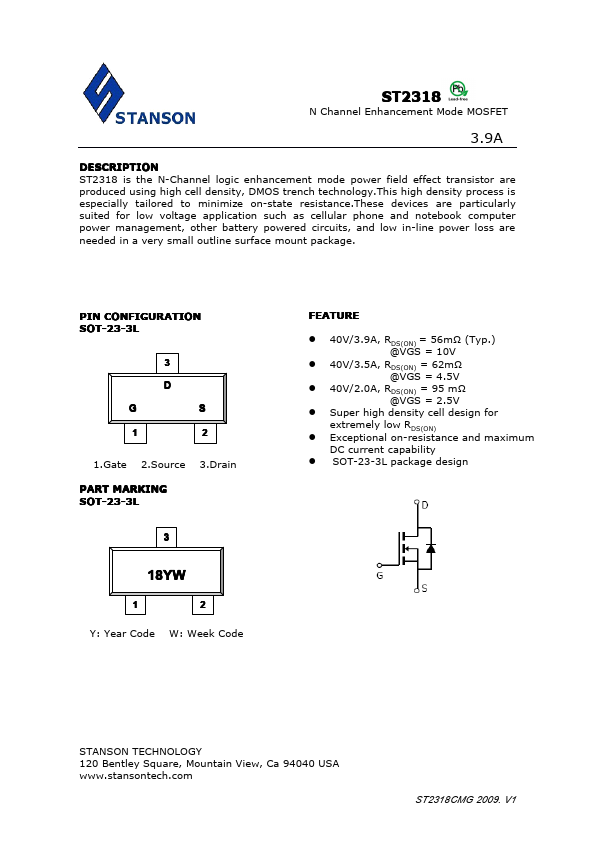

PIN CONFIGURATION SOT-23-3L

3 D

1.Gate 2.Source 3.Drain

PART MARKING SOT-23-3L

18YW

Y: Year Code W: Week Code

FEATURE

- 40V/3.9A, RDS(ON) = 56mΩ (Typ.) @VGS = 10V

- 40V/3.5A, RDS(ON) = 62mΩ @VGS = 4.5V

- 40V/2.0A, RDS(ON) = 95 mΩ @VGS = 2.5V

- Super high density cell design for extremely low RDS(ON)

- Exceptional on-resistance and maximum DC current capability

- SOT-23-3L package design

STANSON TECHNOLOGY 120 Bentley Square, Mountain View, Ca 94040 USA .stansontech.

ST2318CMG 2009....