ST1002

DESCRIPTION

The ST1002 is the N-Channel logic enhancement mode power field effect transistor is produce using high cell density, DMOS trench technology. This high-density process is especially tailored to minimize on-state resistance. These device are particularly suited for low voltage application such as cellular phone and notebook puter power management and other battery powered circuits where high side switching.

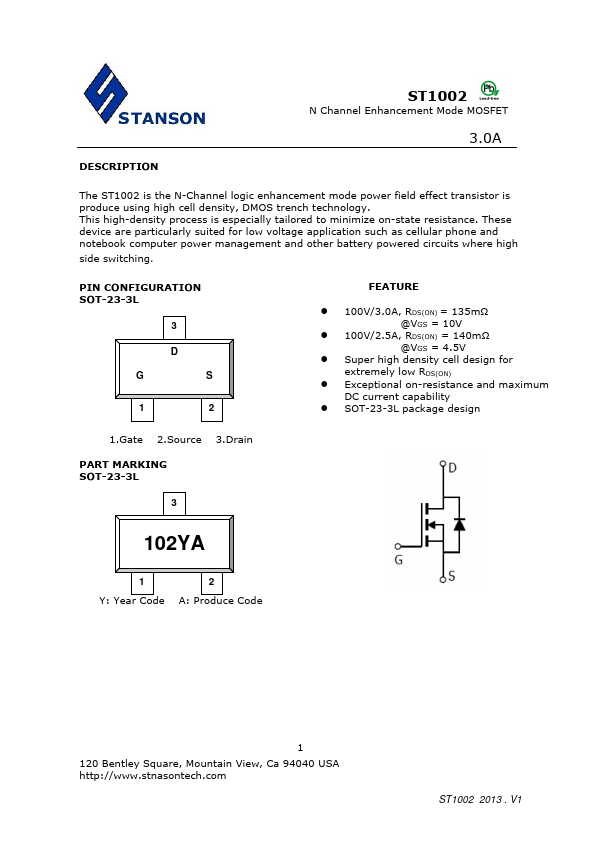

PIN CONFIGURATION SOT-23-3L

FEATURE

100V/3.0A, RDS(ON) = 135mΩ @VGS = 10V

100V/2.5A, RDS(ON) = 140mΩ @VGS = 4.5V

Super high density cell design for extremely low RDS(ON) Exceptional on-resistance and maximum DC current capability SOT-23-3L package design

1.Gate 2.Source 3.Drain

PART MARKING SOT-23-3L

102YA

Y: Year Code A: Produce Code

120 Bentley Square, Mountain View, Ca 94040 USA http://.stnasontech.

ST1002 2013 . V1

N Channel Enhancement Mode MOSFET

3.0A

ABSOULTE MAXIMUM RATINGS (Ta = 25℃ Unless otherwise noted...