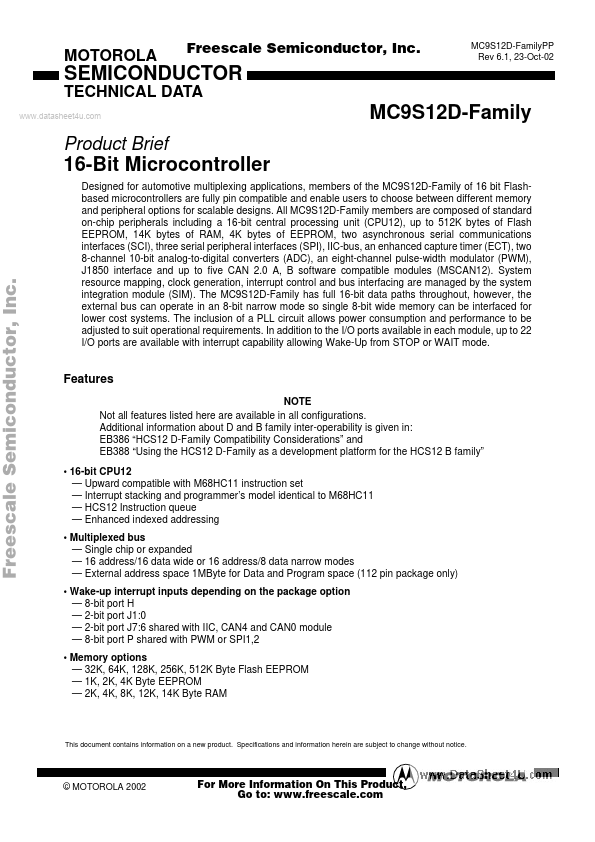

MC9S12D

Features

NOTE Not all features listed here are available in all configurations. Additional information about D and B family inter-operability is given in: EB386 “HCS12 D-Family patibility Considerations” and EB388 “Using the HCS12 D-Family as a development platform for the HCS12 B family”

- 16-bit CPU12

- Upward patible with M68HC11 instruction set

- Interrupt stacking and programmer’s model identical to M68HC11

- HCS12 Instruction queue

- Enhanced indexed addressing

- Multiplexed bus

- Single chip or expanded

- 16 address/16 data wide or 16 address/8 data narrow modes

- External address space 1MByte for Data and Program space (112 pin package only)

- Wake-up interrupt inputs depending on the package option

- 8-bit port H

- 2-bit port J1:0

- 2-bit port J7:6 shared with IIC, CAN4 and CAN0 module

- 8-bit port P shared with PWM or SPI1,2

- Memory options

- 32K, 64K, 128K, 256K, 512K Byte Flash EEPROM

- 1K, 2K, 4K Byte EEPROM

- 2K, 4K, 8K, 12K, 14K Byte RAM

This document contains...