74LS114A

SN54/74LS114A DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP

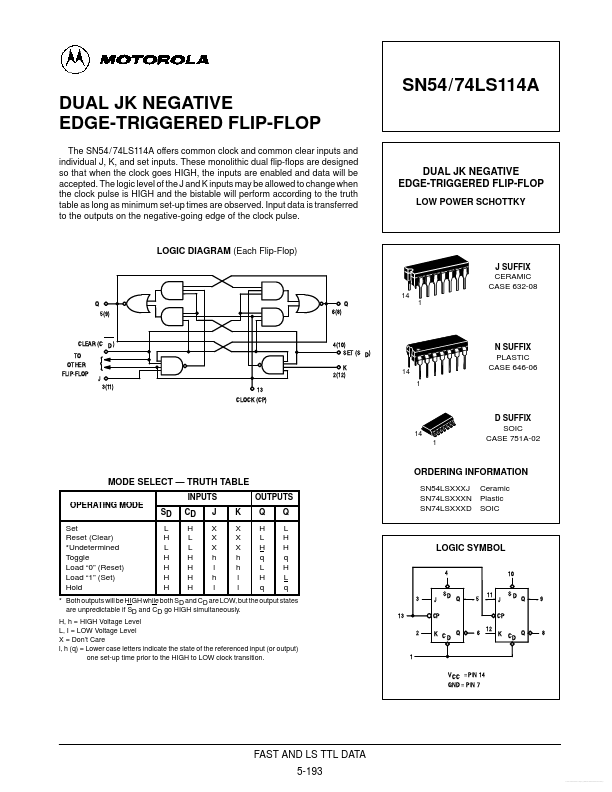

The SN54/ 74LS114A offers mon clock and mon clear inputs and individual J, K, and set inputs. These monolithic dual flip-flops are designed so that when the clock goes HIGH, the inputs are enabled and data will be accepted. The logic level of the J and K inputs may be allowed to change when the clock pulse is HIGH and the bistable will perform according to the truth table as long as minimum set-up times are observed. Input data is transferred to the outputs on the negative-going edge of the clock pulse.

DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP

LOW POWER SCHOTTKY

LOGIC DIAGRAM (Each Flip-Flop)

J SUFFIX CERAMIC CASE 632-08

Q 5(9) 6(8) Q

CLEAR (C TO OTHER FLIPĆFLOP J

)

4(10) SET (S D )

K 2(12) 3(11)

14 1

N SUFFIX PLASTIC CASE 646-06

13 CLOCK (CP)

14 1

D SUFFIX SOIC CASE 751A-02

ORDERING INFORMATION MODE SELECT

- TRUTH TABLE

INPUTS OPERATING MODE SD Set Reset (Clear)

- Undetermined Toggle Load “0” (Reset) Load...