MT58L128L18F

FEATURES w w w

NOT REENDED FOR NEW DESIGNS

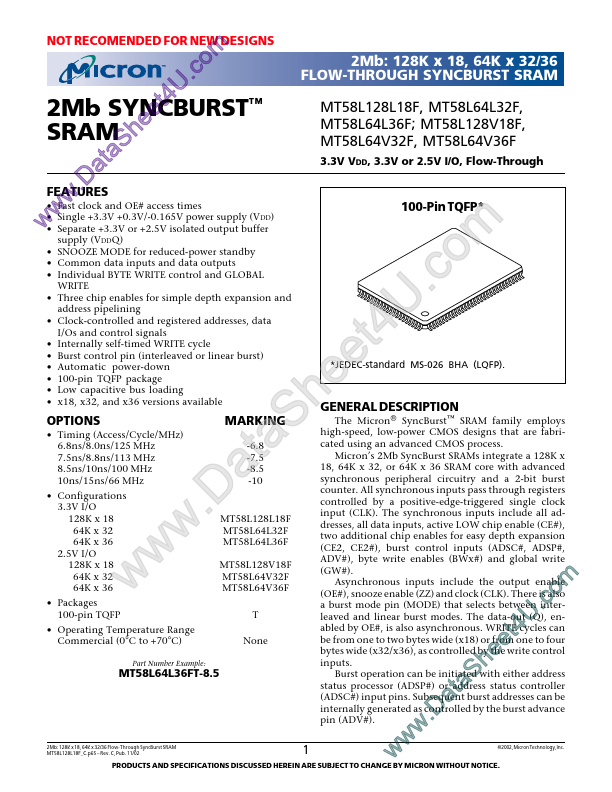

2Mb: 128K x 18, 64K x 32/36 FLOW-THROUGH SYNCBURST SRAM MT58L128L18F, MT58L64L32F, MT58L64L36F; MT58L128V18F, MT58L64V32F, MT58L64V36F

3.3V VDD, 3.3V or 2.5V I/O, Flow-Through

- Fast clock and OE# access times

- Single +3.3V +0.3V/-0.165V power supply (VDD)

- Separate +3.3V or +2.5V isolated output buffer supply (VDDQ)

- SNOOZE MODE for reduced-power standby

- mon data inputs and data outputs

- Individual BYTE WRITE control and GLOBAL WRITE

- Three chip enables for simple depth expansion and address pipelining

- Clock-controlled and registered addresses, data I/Os and control signals

- Internally self-timed WRITE cycle

- Burst control pin (interleaved or linear burst)

- Automatic power-down

- 100-pin TQFP package

- Low capacitive bus loading

- x18, x32, and x36 versions available

OPTIONS

- Timing (Access/Cycle/MHz) 6.8ns/8.0ns/125 MHz 7.5ns/8.8ns/113 MHz 8.5ns/10ns/100 MHz 10ns/15ns/66 MHz

- Configurations 3.3V I/O 128K x 18 64K x 32 64K...