Datasheet Details

- Part number

- ZL30251, ZL30250

- Manufacturer

- Microsemi ↗

- File Size

- 1.18 MB

- Datasheet

- ZL30250-Microsemi.pdf

- Description

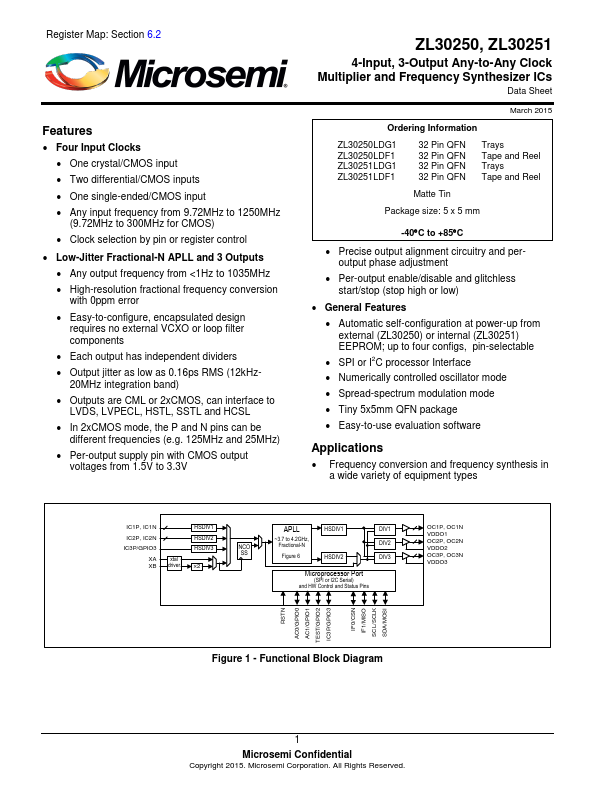

- 3-Output Any-to-Any Clock Multiplier and Frequency Synthesizer

- Note

- This datasheet PDF includes multiple part numbers: ZL30251, ZL30250.

Please refer to the document for exact specifications by model.