Datasheet Details

- Part number

- AS7C33256NTD18A, AS7C33256NTD16A

- Manufacturer

- Alliance Semiconductor

- File Size

- 162.97 KB

- Datasheet

- AS7C33256NTD16A-AllianceSemiconductor.pdf

- Description

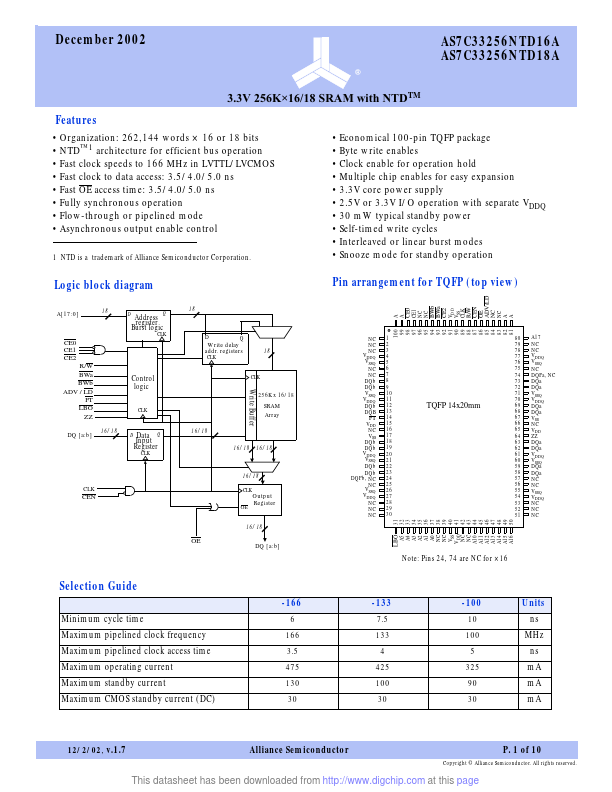

- 3.3V 256K X 16/18 SRAM

- Note

- This datasheet PDF includes multiple part numbers: AS7C33256NTD18A, AS7C33256NTD16A.

Please refer to the document for exact specifications by model.