Description

8

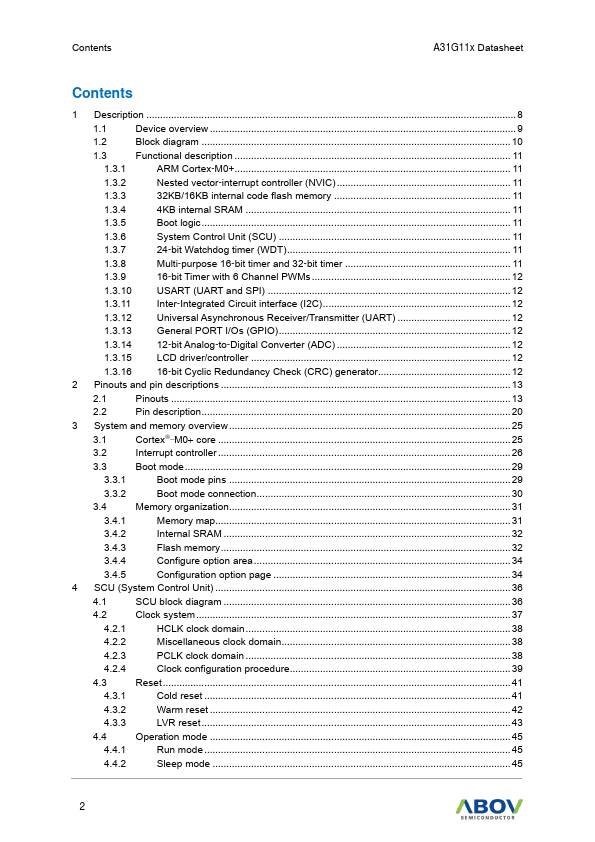

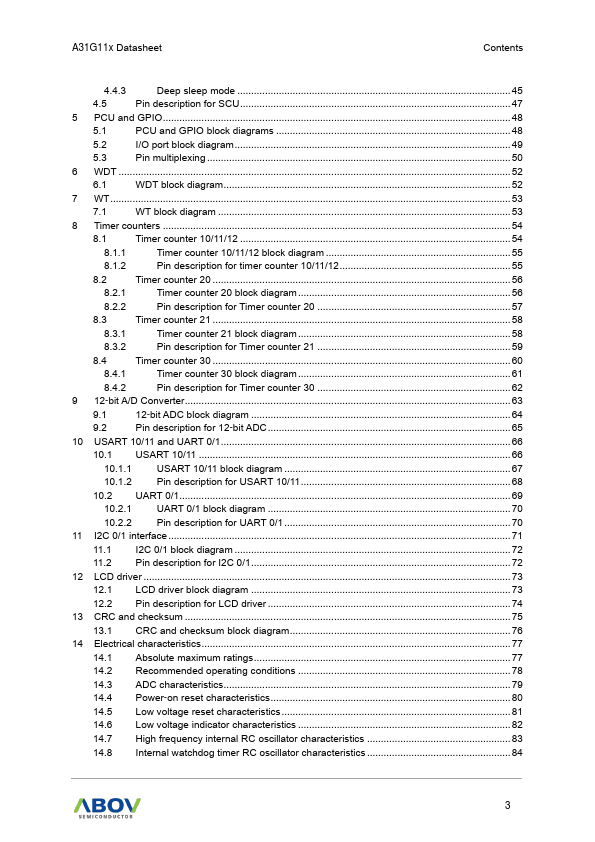

1.1

Device overview 9

1.2

Block diagram 10

1.3

Functional description 11

1.3.1

ARM Cortex-M0+ 11

1.3.2

Nested vector-interrupt controller (NVIC) 11

1.3.3

32KB/16KB internal code flash memory 11

1.3.4

4KB internal SRAM 11

1.3.5

Boot logic 11

1.3.6

System Control Unit (SCU) 11

1.3.7

24-bit Watchdog timer (WDT) 11

1.3.8

Multi-purpose 16-bit timer and 32-bit timer 11

1.3.9

16-bit Timer with 6 Channel PWMs 12

1.3.10 USART (UART and SPI) 12

1.3.11

Inter-Integra

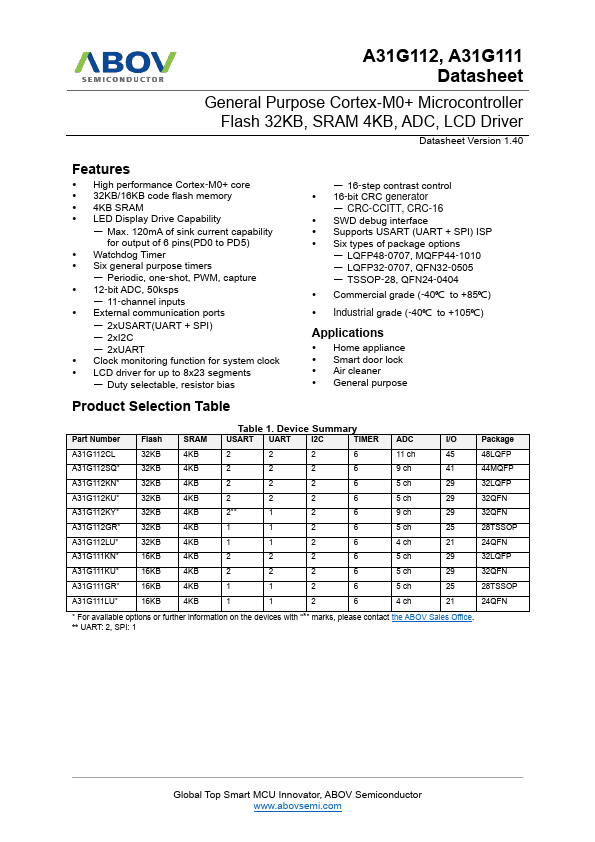

Features

- High performance Cortex-M0+ core.

- 32KB/16KB code flash memory.

- 4KB SRAM.

- LED Display Drive Capability.

- Max. 120mA of sink current capability for output of 6 pins(PD0 to PD5).

- Watchdog Timer.

- Six general purpose timers.

- Periodic, one-shot, PWM, capture.

- 12-bit ADC, 50ksps.

- 11-channel inputs.

- External communication ports.

- 2xUSART(UART + SPI).

- 2xI2C.

- 2xUART.

- Clock monitoring function for system clock.