SN65DSI86

SN65DSI86 is MIPI DSI to eDP Bridge manufactured by Texas Instruments.

Features

- Embedded Display Port™ ( e DP™) 1.4 pliant supporting 1, 2, or 4 lanes at 1.62 Gbps (RBR), 2.16 Gbps, 2.43 Gbps, 2.7 Gbps (HBR), 3.24 Gbps, 4.32 Gbps, or 5.4 Gbps (HBR2).

- Implements MIPI® D-PHY version 1.1 physical layer front-end and display serial interface (DSI) version 1.02.00

- Dual-channel DSI receiver configurable for one, two, three, or four D-PHY data lanes per channel operating up to 1.5 Gbps per lane

- Supports 18 bpp and 24 bpp DSI video packets with RGB666 and RGB888 formats

- Suitable for 60 fps 4K 4096 × 2304 resolution at 18 bpp color, and WUXGA 1920 × 1200 resolution with 3D graphics at 60 fps (120 fps equivalent)

- MIPI front-end configurable for single-channel or dual-channel DSI configuration

- Supports dual-channel DSI odd, even and left, right operating modes

- 1.2-V main VCC power supply and 1.8-V supply for digital I/Os

- Low-power features include panel refresh and MIPI ultralow power state (ULPS) support

- Display Port lane polarity and assignment configurable.

- Supports 12-MHz, 19.2-MHz, 26-MHz, 27-MHz, and 38.4-MHz frequencies through external reference clock (REFCLK)

- ESD rating ±4 k V (HBM)

- Packaged in 64ball 5-mm x 5-mm n FBGA (ZXH)

- I2C configurable

- Temperature range:

- 40°C to +85°C

2 Applications

- PC & notebooks

- Tablets

- Retail automation & payment

- Test and measurement

- Factory automation and control

3 Description

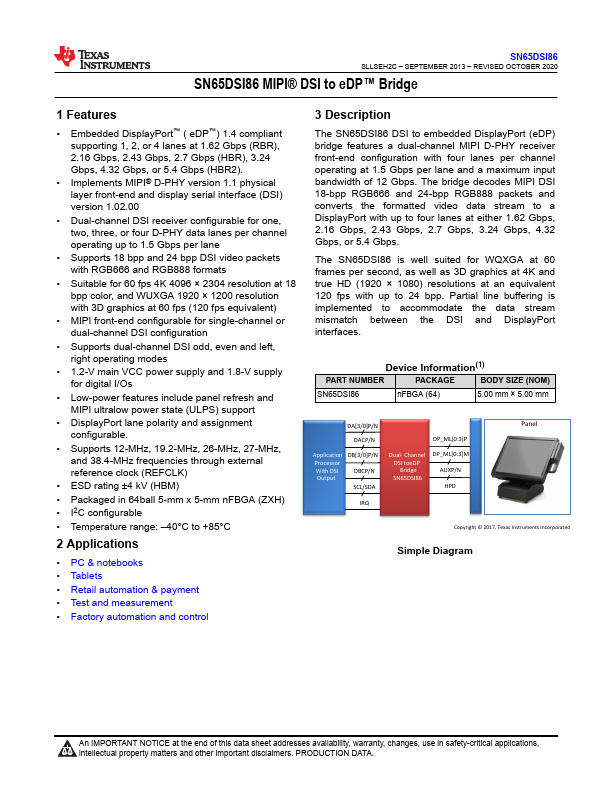

The SN65DSI86 DSI to embedded Display Port (e DP) bridge features a dual-channel MIPI D-PHY receiver front-end configuration with four lanes per channel operating at 1.5 Gbps per lane and a maximum input bandwidth of 12 Gbps. The bridge decodes MIPI DSI 18-bpp RGB666 and 24-bpp RGB888 packets and converts the formatted video data stream to a Display Port with up to four lanes at either 1.62 Gbps, 2.16 Gbps, 2.43 Gbps, 2.7 Gbps, 3.24 Gbps, 4.32 Gbps, or 5.4 Gbps.

The SN65DSI86 is well suited for WQXGA at 60 frames per second, as well as 3D graphics at 4K and true HD (1920 × 1080) resolutions at an...