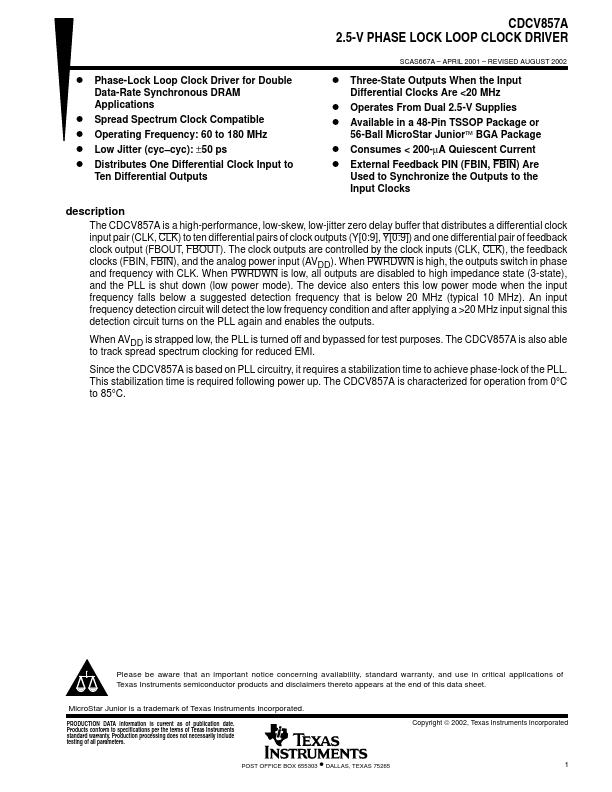

- Part: CDCV857A

- Description: 2.5-V PHASE LOCK LOOP CLOCK DRIVER

- Manufacturer: Texas Instruments

- Size: 829.53 KB

Related Texas Instruments Datasheets

| Part Number | Description |

|---|---|

| CDCV857B | 2.5-V PHASE LOCK LOOP CLOCK DRIVER |

| CDCV857BI | 2.5-V PHASE LOCK LOOP CLOCK DRIVER |

| CDCV850 | 2.5-V Phase Lock Loop Clock Driver |

| CDCV850I | 2.5-V Phase Lock Loop Clock Driver |

| CDCV855 | 2.5-V PHASE-LOCK LOOP CLOCK DRIVER |