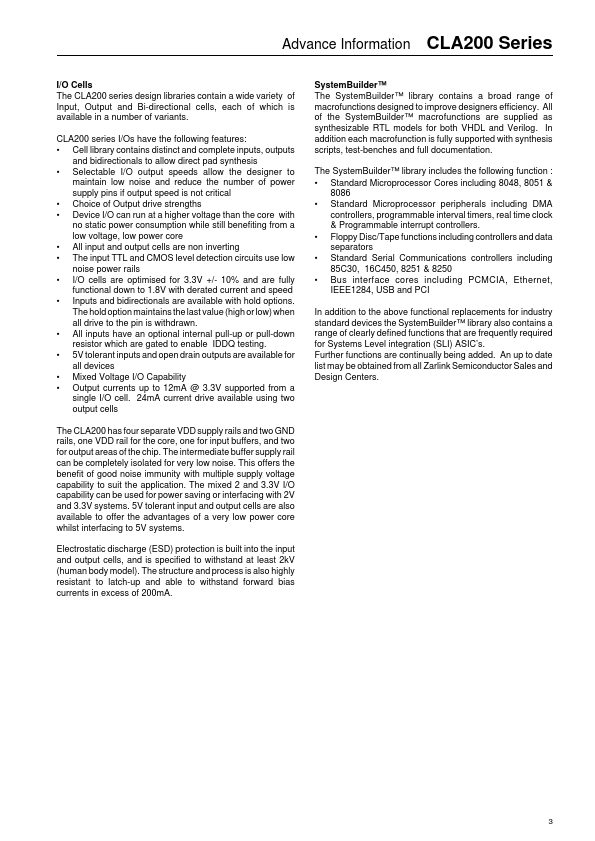

Datasheet Summary

( DataSheet : .. )

CLA200 Series

CMOS Gate Arrays Advance Information

DS4812 ISSUE 1.3 July 1997

INTRODUCTION

The CLA200 Series Arrays from Zarlink Semiconductor offer designers the capability to integrate designs of more than 2 million gates. There are 14 fixed arrays optimised for low to medium plexity designs ranging from 11K used gates up to 628K used gates. For larger designs optimised arrays can be built with up to 3 million available gates. Using automated gate array base constructor software, a tailor made optimised gate array can be built to customers requirements which gives designers the ability to specify the optimum die size whilst retaining the benefits...