LH540205 Key Features

- Fast Access Times: 20/25/35/50 ns

- Fast-Fall-Through Time Architecture Based on CMOS Dual-Port SRAM Technology

- Input Port and Output Port Have Entirely Independent Timing

- Expandable in Width and Depth

- Full, Half-Full, and Empty Status Flags

- Data Retransmission Capability

- TTL-patible I/O

- Pin and Functionally patible with Am/IDT7205

- Control Signals Assertive-LOW for Noise Immunity

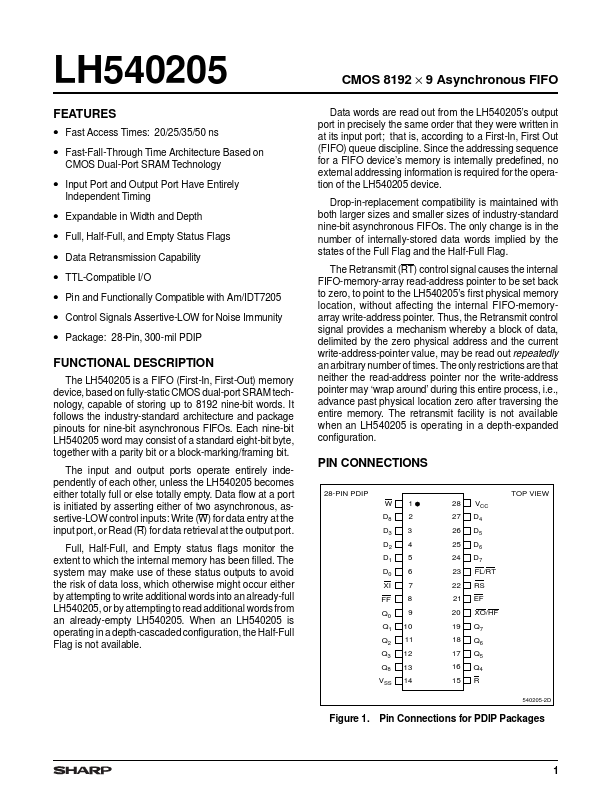

- Package: 28-Pin, 300-mil PDIP