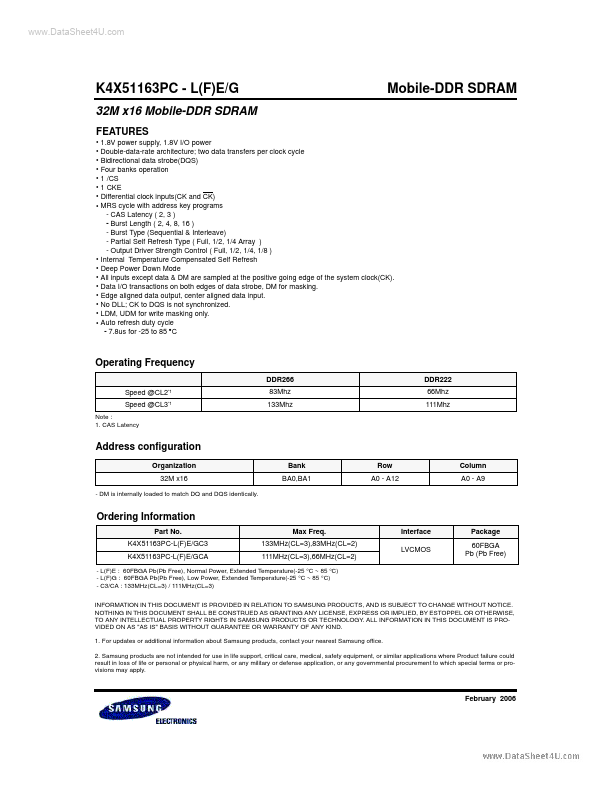

K4X51163PC Overview

Key Specifications

Package: FBGA

Operating Voltage: 1.8 V

Max Frequency: 111 MHz

Max Operating Temp: 85 °C

Key Features

- 1.8V power supply, 1.8V I/O power

- Double-data-rate architecture; two data transfers per clock cycle

- Bidirectional data strobe(DQS)

- Four banks operation

- Differential clock inputs(CK and CK)