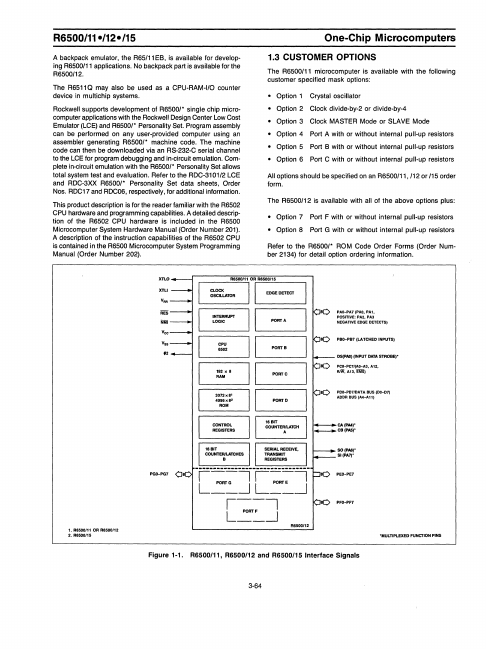

R6500-11 Key Features

- Enhanced 6502 CPU -Four new bit manipulation instructions: Set Memory Bit (SMB) Reset Memory Bit (RMB) Branch on Bit Set

- 3K-byte mask-programmable ROM (R6500/11, R6500/12)

- 4K-byte mask-programmable ROM (R6500/15)

- 192-byte static RAM

- 32 TIL-patible 110 lines (R6500/11, R6500/15)

- 56 TIL-patible 110 lines (R6500/12)

- One 8-bit port may be tri-stated under software control

- One 8-bit port with programmable latched input

- Two 16-bit programmable counter/timers, with latches

- Pulse width measurement -Asymmetrical pulse generation -Pulse generation -Interval timer -Event counter -Retriggerable i