IDT2305A Key Features

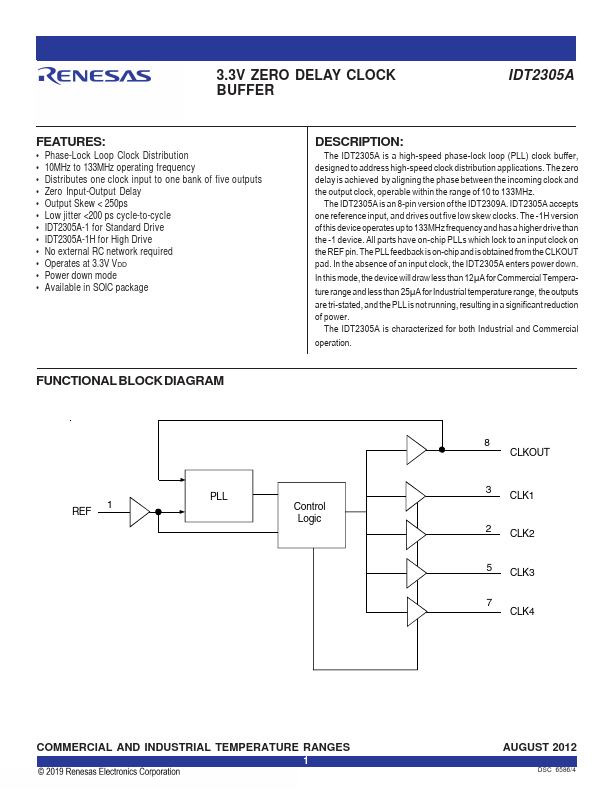

- Phase-Lock Loop Clock Distribution

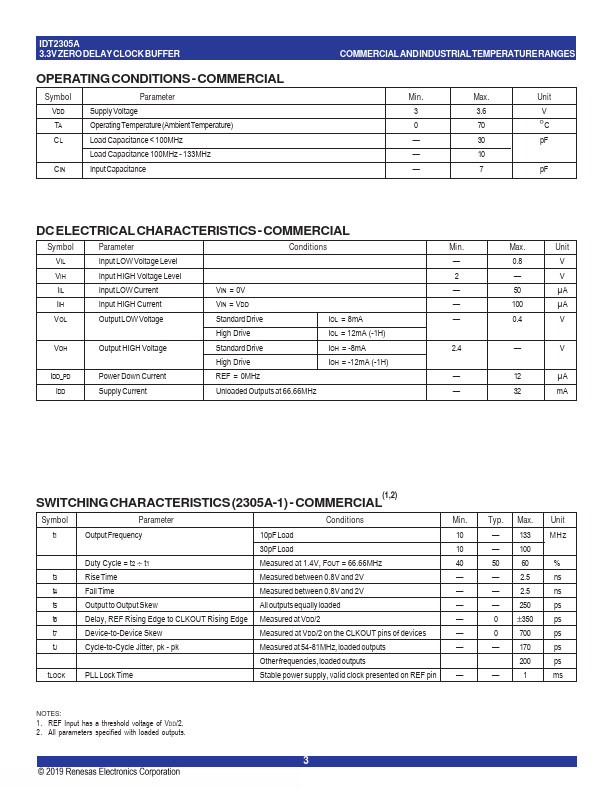

- 10MHz to 133MHz operating frequency

- Distributes one clock input to one bank of five outputs

- Zero Input-Output Delay

- Output Skew < 250ps

- Low jitter <200 ps cycle-to-cycle

- IDT2305A-1 for Standard Drive

- IDT2305A-1H for High Drive

- No external RC network required

- Operates at 3.3V VDD