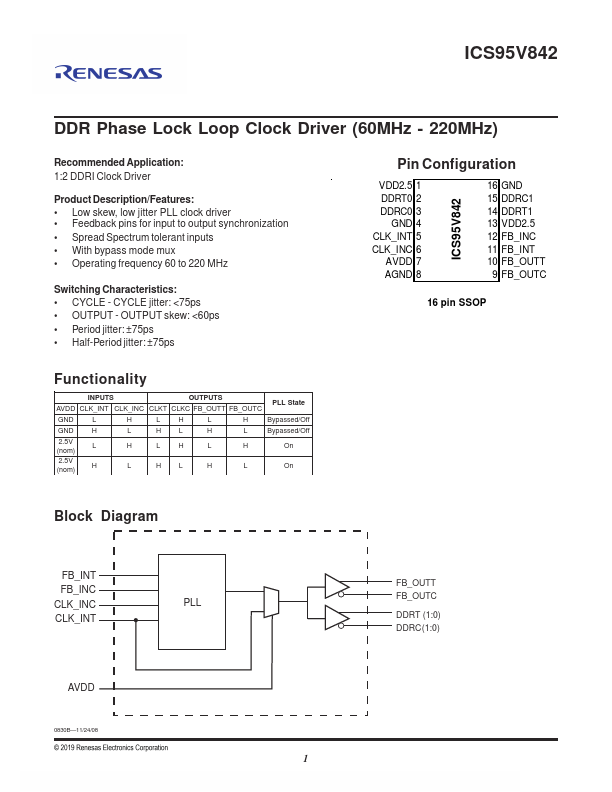

ICS95V842

Description

Power supply, nominal 2.5V "True" Clock of differential pair output. "Complementary" Clock of differential pair output. Ground pin. "True" reference clock input. "Complementary" reference clock input. 3.3V Analog Power pin for Core PLL Analog Ground pin for Core PLL Complement single-ended feedback output, dedicated external feedback.

Key Features

- Low skew, low jitter PLL clock driver

- Feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- With bypass mode mux

- Operating frequency 60 to 220 MHz Switching Characteristics:

- CYCLE - CYCLE jitter: <75ps

- OUTPUT - OUTPUT skew: <60ps

- Period jitter: ±75ps

- Half-Period jitter: ±75ps