ICS663 Overview

Description

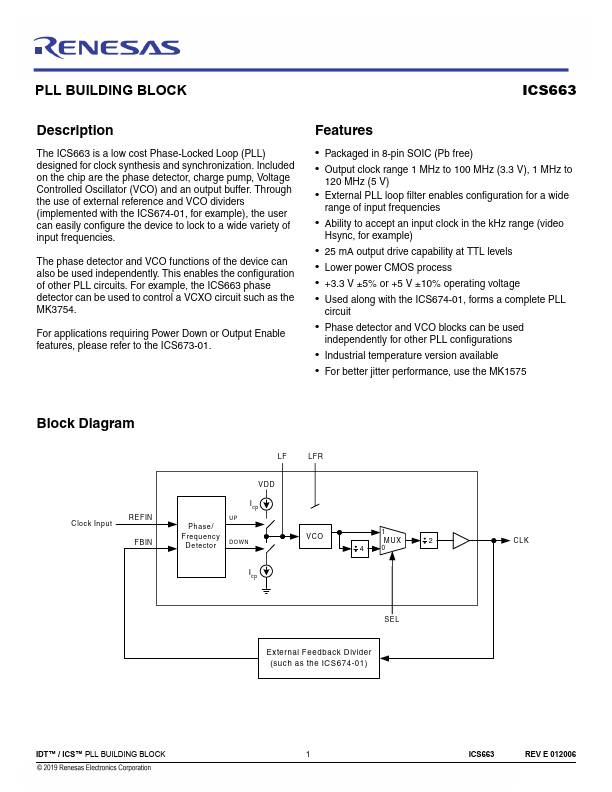

The ICS663 is a low cost Phase-Locked Loop (PLL) designed for clock synthesis and synchronization. Included on the chip are the phase detector, charge pump, Voltage Controlled Oscillator (VCO) and an output buffer.

Key Features

- Packaged in 8-pin SOIC (Pb free)

- Output clock range 1 MHz to 100 MHz (3.3 V), 1 MHz to 120 MHz (5 V)

- External PLL loop filter enables configuration for a wide range of input frequencies

- Ability to accept an input clock in the kHz range (video Hsync, for example)

- 25 mA output drive capability at TTL levels

- Lower power CMOS process

- +3.3 V ±5% or +5 V ±10% operating voltage

- Used along with the ICS674-01, forms a complete PLL circuit

- Phase detector and VCO blocks can be used independently for other PLL configurations

- Industrial temperature version available