HYB18T512161BF Datasheet Text

December 2006

..

HYB18T 512161 B F

512-Mbit x16 DDR2 SDRAM DDR2 SDRAM RoHS pliant

Internet Data Sheet

Rev. 1.43

Internet Data Sheet

..

HYB18T512161BF- 20/22/25/28/33 512-Mbit Double-Data-Rate-Two SDRAM

HYB18T512161BF Revision History: 2006-11, Rev. 1.43 Page All 94-101 82-86 All All 9 86 77

- 80 67 71 76 77 78 86 Subjects (major changes since last revision) Adapted internet edtion added chapter 7 explaining AC timing measurement condition (reference load ; slew rate ; set up & hold timing references ; derating values for input /mand ,data ) setup & hold timings are changed with reference to Industrial standard definition removed all the occurances of RDQS as it in not used in graphics (x16) Qimonda Update added power supply info for [-20 and -22] table 41: change IDD max to IDD typ Corrected AC Timing values for -20 speedsort in table 35 and table 36 table 18: added speed sort -20 table 24: added speed sort -20 table 33 and table 34: added speed sort -20 table 35: change CL=7 2.0 tCK (speed sort -20) table 36: added all values for speed sort -20 table 41: added all IDD values (all speed sorts)

Previous Revision: 2006-09, Rev. 1.32 Previous Revision: 2006-03, Rev. 1.31

Previous Revision: 2006-02, Rev. 1.21

We Listen to Your ments Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: techdoc@qimonda. qag_techdoc_rev400 / 3.2 QAG / 2006-08-01 03292006-L40N-L04G

2

Internet Data Sheet

..

HYB18T512161BF- 20/22/25/28/33 512-Mbit Double-Data-Rate-Two SDRAM

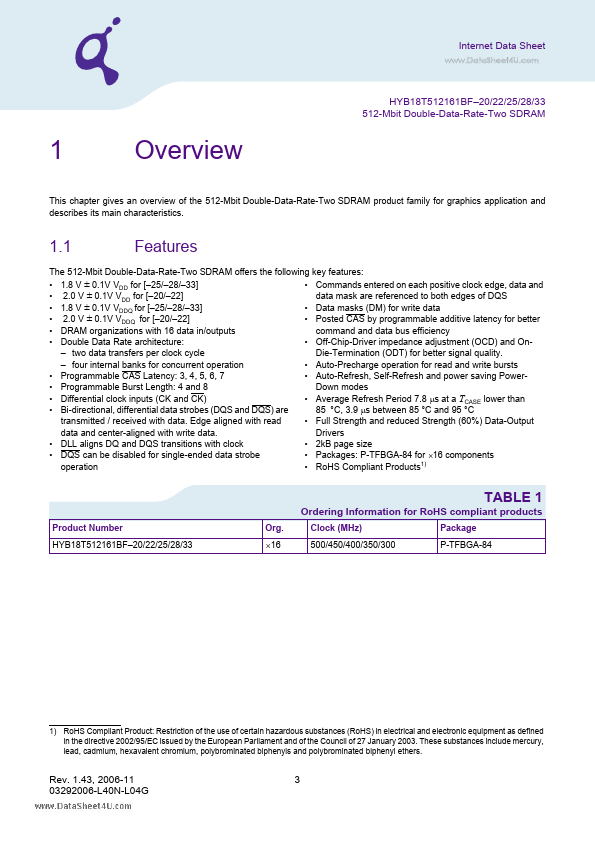

1

Overview

This chapter gives an overview of the 512-Mbit...