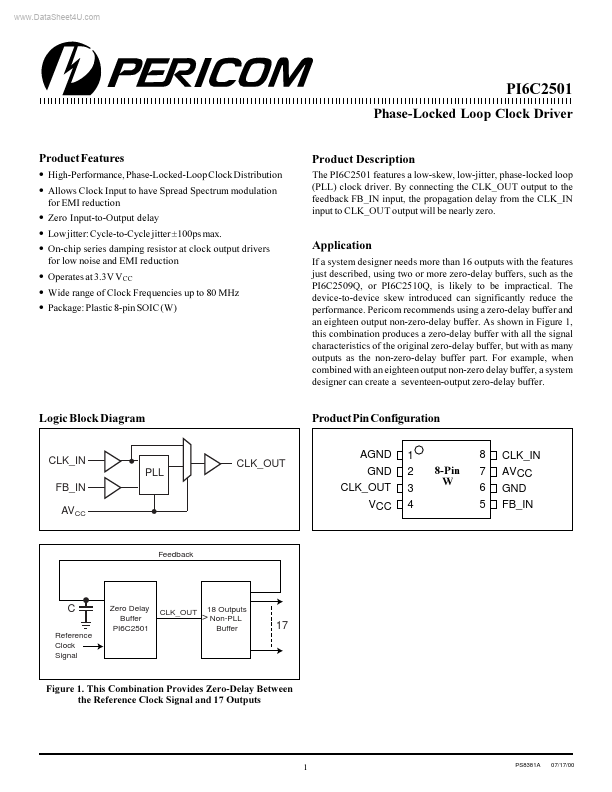

PI6C2501 Overview

Key Specifications

Package: SOP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Key Features

- High-Performance, Phase-Locked-Loop Clock Distribution

- Allows Clock Input to have Spread Spectrum modulation for EMI reduction

- Zero Input-to-Output delay

- Low jitter: Cycle-to-Cycle jitter ±100ps max

- On-chip series damping resistor at clock output drivers for low noise and EMI reduction

- Operates at 3.3V VCC

- Wide range of Clock Frequencies up to 80 MHz

- Package: Plastic 8-pin SOIC (W)