Datasheet Summary

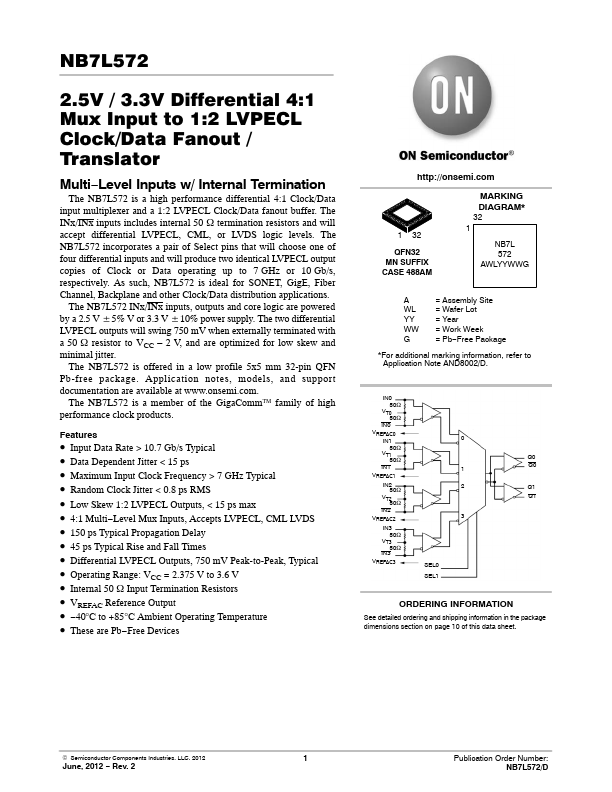

2.5V / 3.3V Differential 4:1 Mux Input to 1:2 LVPECL Clock/Data Fanout / Translator

Multi- Level Inputs w/ Internal Termination

The NB7L572 is a high performance differential 4:1 Clock/Data input multiplexer and a 1:2 LVPECL Clock/Data fanout buffer. The INx/INx inputs includes internal 50 W termination resistors and will accept differential LVPECL, CML, or LVDS logic levels. The NB7L572 incorporates a pair of Select pins that will choose one of four differential inputs and will produce two identical LVPECL output copies of Clock or Data operating up to 7 GHz or 10 Gb/s, respectively. As such, NB7L572 is ideal for SONET, GigE, Fiber Channel, Backplane and other Clock/Data...