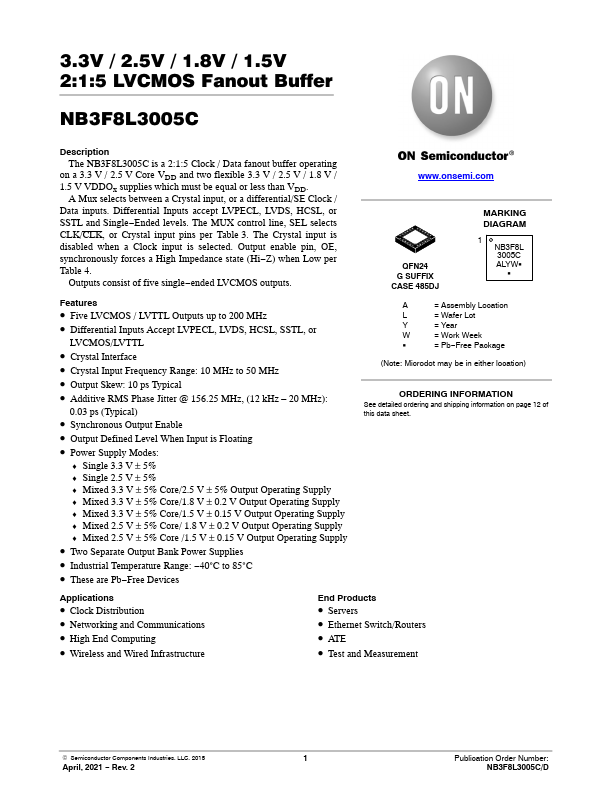

| Part | NB3F8L3005C |

|---|---|

| Description | 2:1:5 LVCMOS Fanout Buffer |

| Manufacturer | onsemi |

| Size | 250.55 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74HC125 | NXP Semiconductors | Quad buffer/line driver |

| BUF04 | Analog Devices | Closed-Loop High Speed Buffer |

| BUF03 | Analog Devices | High Speed Voltage Follower/Buffer |