Part number:

M2S56D20AKT-75L, M2S

Manufacturer:

Mitsubishi

File Size:

768.53 KB

Description:

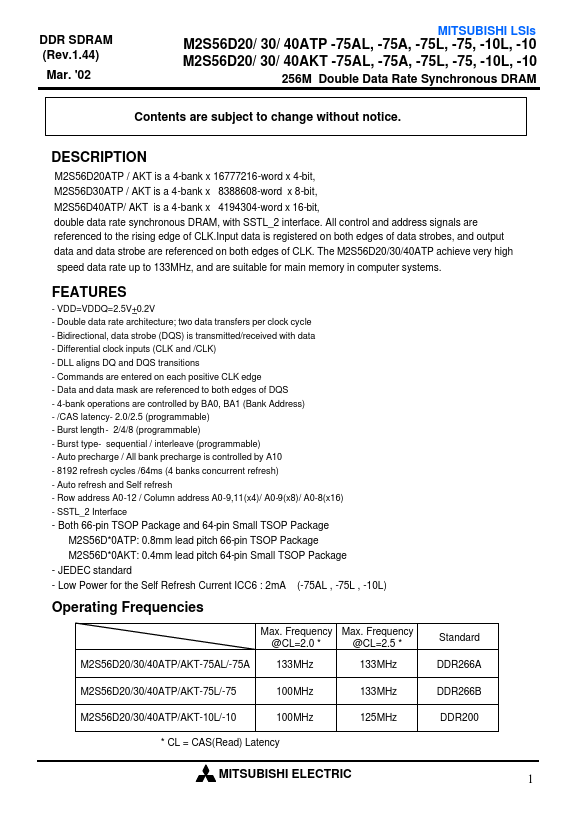

256m double data rate synchronous dram.

Note:

This datasheet PDF includes multiple part numbers: M2S56D20AKT-75L, M2S.

Please refer to the document for exact specifications by model.