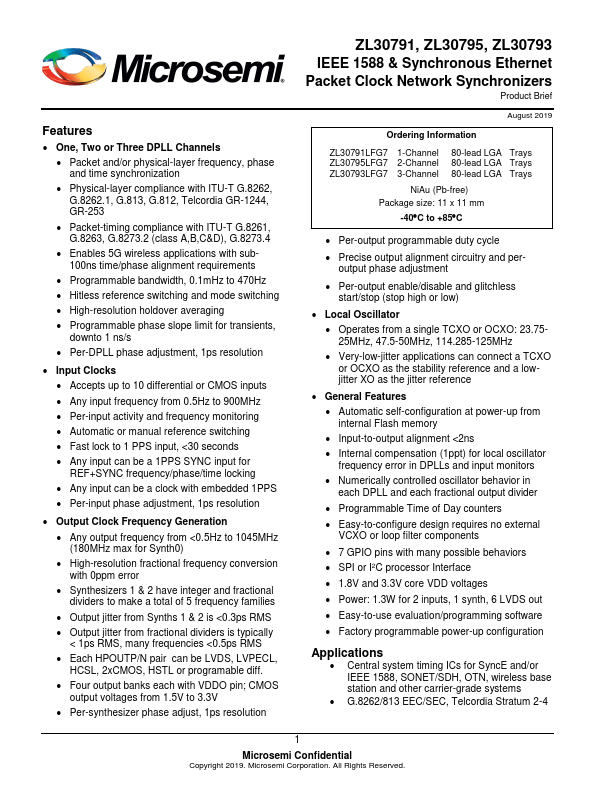

ZL30793 Overview

Key Specifications

Pins: 80

Key Features

- One, Two or Three DPLL Channels

- Packet and/or physical-layer frequency, phase and time synchronization

- Physical-layer compliance with ITU-T G.8262, G.8262.1, G.813, G.812, Telcordia GR-1244, GR-253

- Packet-timing compliance with ITU-T G.8261, G.8263, G.8273.2 (class A,B,C&D), G.8273.4

- Enables 5G wireless applications with sub100ns time/phase alignment requirements