Datasheet Summary

Features

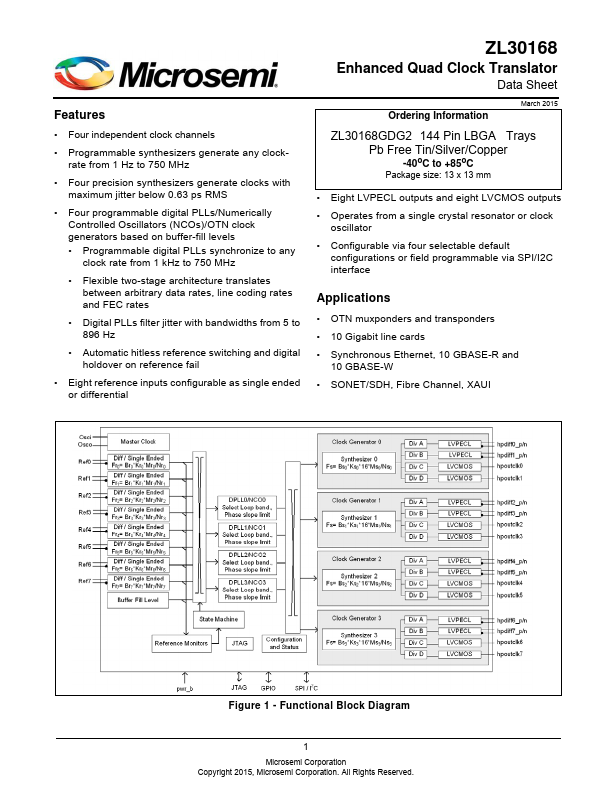

- Four independent clock channels

- Programmable synthesizers generate any clockrate from 1 Hz to 750 MHz

- Four precision synthesizers generate clocks with maximum jitter below 0.63 ps RMS

- Four programmable digital PLLs/Numerically Controlled Oscillators (NCOs)/OTN clock generators based on buffer-fill levels

- Programmable digital PLLs synchronize to any clock rate from 1 kHz to 750 MHz

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter with bandwidths from 5 to 896 Hz

- Automatic hitless reference switching and digital holdover on reference fail

- Eight reference inputs configurable as single...