SY100EP195V Overview

Key Specifications

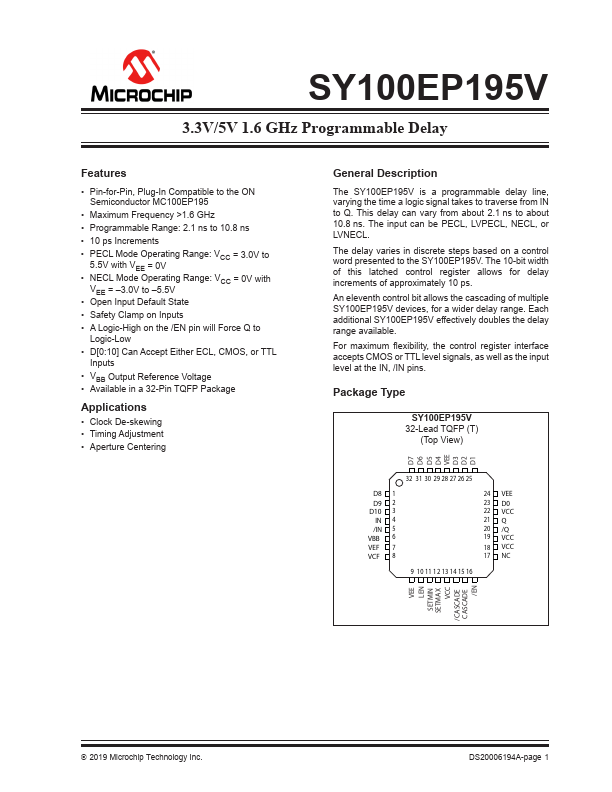

Package: TQFP

Mount Type: Surface Mount

Pins: 32

Max Voltage (typical range): 5.5 V

Description

The SY100EP195V is a programmable delay line, varying the time a logic signal takes to traverse from IN to Q. This delay can vary from about 2.1 ns to about 10.8 ns.

Key Features

- Pin-for-Pin, Plug-In Compatible to the ON Semiconductor MC100EP195

- Maximum Frequency >1.6 GHz

- Programmable Range: 2.1 ns to 10.8 ns

- 10 ps Increments

- PECL Mode Operating Range: VCC = 3.0V to 5.5V with VEE = 0V