ISPCLOCK5500 Overview

Key Features

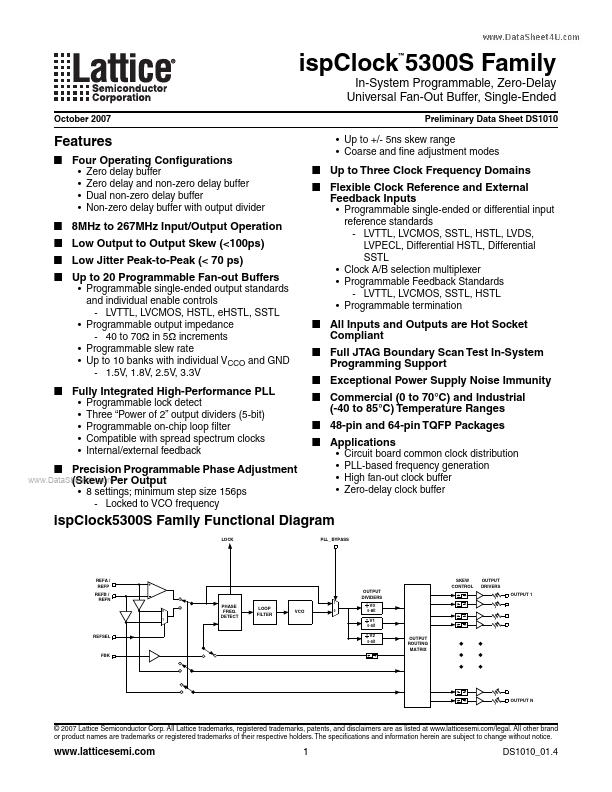

- Four Operating Configurations

- Zero delay buffer Zero delay and non-zero delay buffer Dual non-zero delay buffer Non-zero delay buffer with output divider

- Up to +/- 5ns skew range

- Coarse and fine adjustment modes

- Up to Three Clock Frequency Domains