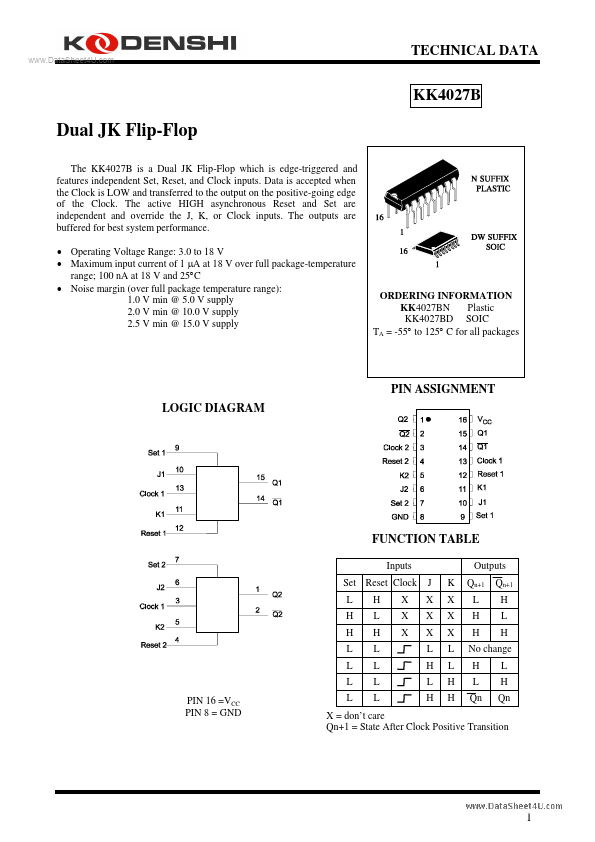

KK4027B Overview

Key Features

- Operating Voltage Range: 3.0 to 18 V

- Maximum input current of 1 µA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (over full package temperature range): 1.0 V min @ 5.0 V supply 2.0 V min @ 10.0 V supply 2.5 V min @ 15.0 V supply