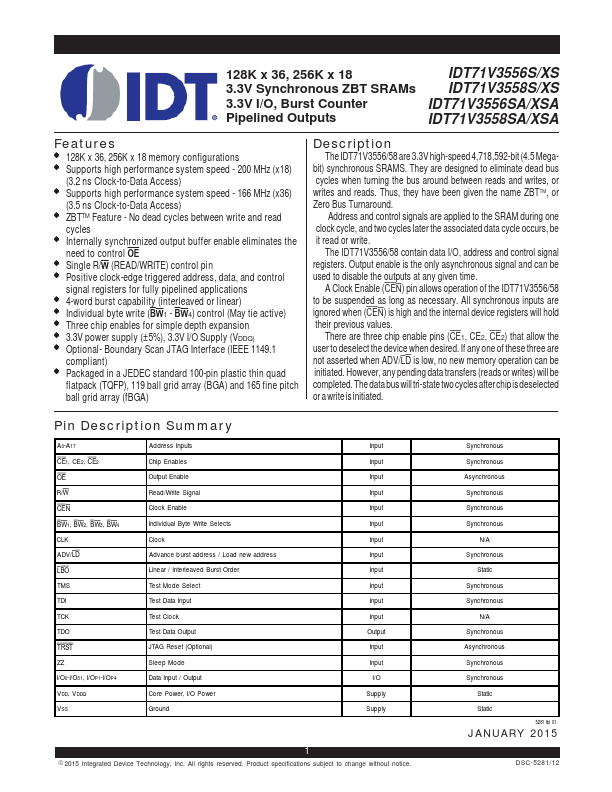

| Part | IDT71V3556XS |

|---|---|

| Description | 3.3V Synchronous ZBT SRAMs |

| Manufacturer | IDT |

| Size | 490.25 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT71V3556S | Integrated Device Technology | 3.3V Synchronous ZBT SRAMs |

| IDT71V3556SA | Integrated Device Technology | 3.3V Synchronous ZBT SRAMs |

| IDT71V3558S | Integrated Device Technology | 3.3V Synchronous ZBT SRAMs |

| IDT71V3558SA | Integrated Device Technology | 3.3V Synchronous ZBT SRAMs |