GS8150V36AB-300

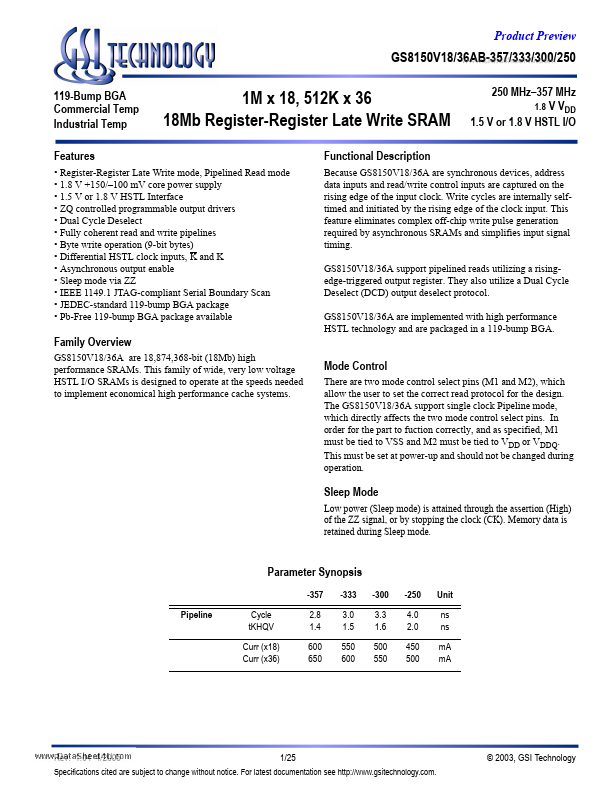

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V36AB-333

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V36AB-357

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V18AB-250

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V18AB-300

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V18AB-333

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS8150V18AB-357

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)

GS815018AB-250

1M x 18/ 512K x 36 18Mb Register-Register Late Write SRAM (GSI Technology)